ISSCC 2019论文之引人瞩目的高速接口

编者按:ISSCC会议在集成电路设计的地位无容置疑。ISSCC2019刚刚结束,接下来我将在公众号开启一个新的系列,跟大家一起来读今年的ISSCC论文。今天先来看看第6个session Ultra-High-Speed Wireline都讲了些什么。

100G的RX另一个难点是CTLE,又要宽带、又要Peaking可调、又要保持线性度,设计难度很高。这篇里面没有集成CTLE。

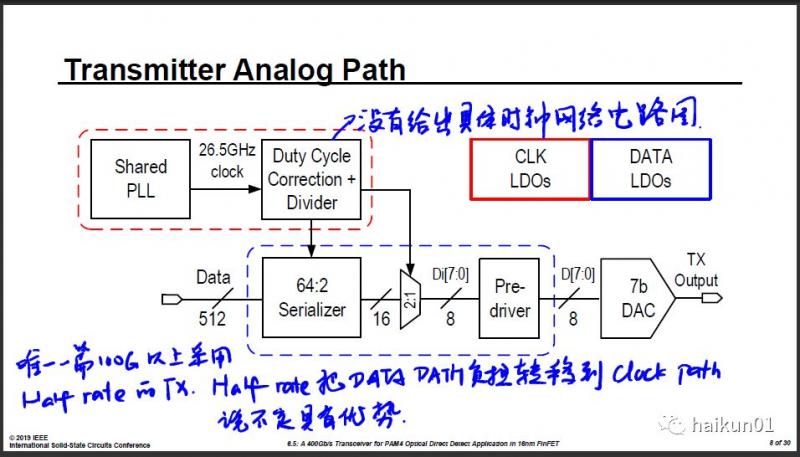

TX方面这篇选择了Half Rate结构,这是在超过100G的TX里唯一一篇Half Rate的结构。Half Rate和Quad Rate相比,时钟的频率更高,因此更难传输。但是它简化了MUX的设计,最后一级MUX是只需要2:1即可,这是TX里速度最高的节点,2:1相比于4:1可以减小很多寄生电容。尽管大部分100G TX选择了Quad Rate,但我觉得不一定就比Half Rate有优势。毕竟时钟通路只需要单频(窄带)即可,而数据通路是宽带的。窄带电路比宽带电路容易设计多了。这样Half Rate实际上是把宽带通路上的负担转移到窄带上来,应该带来优势才对。一般说传25GHz的时钟太费电,但如果可以加电感和传输线做谐振的话,其实时钟传输网络耗电量不会特别大。可惜这篇没有给出时钟和MUX电路的具体实现。

TX里还用到了一个小技术,通过正反馈来提高反相器的速度,使上升下降沿更陡峭,其实有点类似均衡的概念。去年ISSCC有两篇采用了类似做法。我仿过这样的结构,应该是有效的,但要消耗更多功耗。

6)128Gb/s TX from IBM

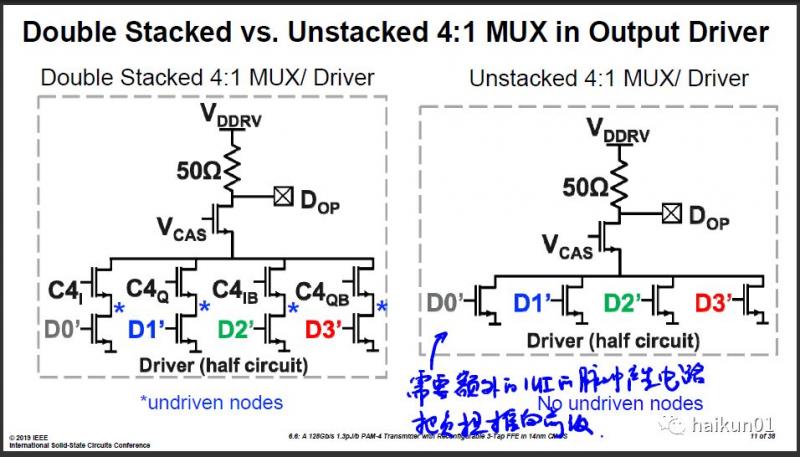

这篇的亮点在于对4:1 MUX的优化。TX的结构和去年Intel的112G比较接近,也是采用CML的Driver。提一句,在56G采用SST作为TX Driver的居多。

高速串口的TX基本上就是一个Serilizer再加一个Driver。越往前速度越低,所以我们应该尽量简化后级,把负担推往前级速度比较低比较好处理的地方。这篇大致是这个思路。在MUX这一级去掉了Stack的时钟晶体管,而在前级添加一些逻辑产生1UI的脉冲信号。

很多时候电路的优化都是在一个个trade-off之间做取舍。宏观的指导思想就是把负担留给更容易解决的地方去解决。这篇是把负担推向前级速度较慢的电路,上一篇是把负担推向窄带的时钟路径。

7)112G TX in 40nm CMOS from Yuan Ze University

这是来自台湾学术界的一篇论文,用40nm做出了112G的TX,非常令人印象深刻。话说我跟此文作者之前认识,碰过几次面,还一起流过一次片。这篇论文即反映了学术界的无奈也反映了学术界应该选的方向。无奈在于拿不到/负担不起最先进的工艺,只能在落后工艺下进行竞争;方向在于学术界还是应该追求极致优化,以展现技术为主。

凭空想一想,假如让我在学校设计112G的TX的话:第一,FFE是必须的,否则眼睛打不开,没法展现效果;第二,不要在乎可靠性,选择金属走线宽度时只考虑性能因素,宁愿线被烧断也要减小寄生电容;第三,不要选择TX-DAC的结构,或者不要使用thermal code结构,将小cell合并成大cell,牺牲匹配换取速度;第四,适当的提高电源电压;第五,只在低速点位设置可调,如偏置电压等等,我们负担不起在高速路径上可调的成本。有了这些,应该勉强可以用落后工艺去拼一拼速度吧……

8)36Gb/s Adaptive CDR from University of Toronto

这篇略过……

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码