ISSCC 2019论文之引人瞩目的高速接口

编者按:ISSCC会议在集成电路设计的地位无容置疑。ISSCC2019刚刚结束,接下来我将在公众号开启一个新的系列,跟大家一起来读今年的ISSCC论文。今天先来看看第6个session Ultra-High-Speed Wireline都讲了些什么。

ISSCC论文解析目录:

Session 6 Ultra-High-Speed Wireline

ISSCC会议在集成电路设计的地位无容置疑。ISSCC2019刚刚结束,接下来我将在公众号开启一个新的系列,跟大家一起来读今年的ISSCC论文。今天先来看看第6个session Ultra-High-Speed Wireline都讲了些什么。

在今年的ISSCC上,高速接口(wireline)方向受到了极大的关注。除了有两个session的论文,在傍晚的现场展示环节,据我目测除了AI相关的芯片之外,最多的就是高速接口了,同时第一天的tutorial和最后一天的forum,也各有一个与高速串口相关。

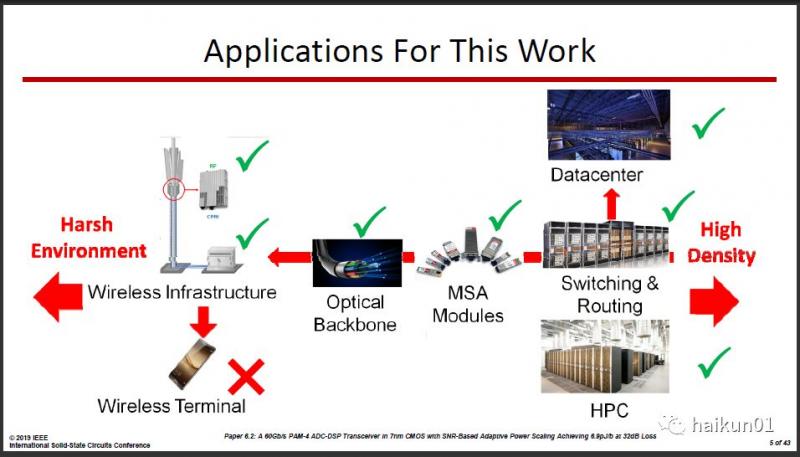

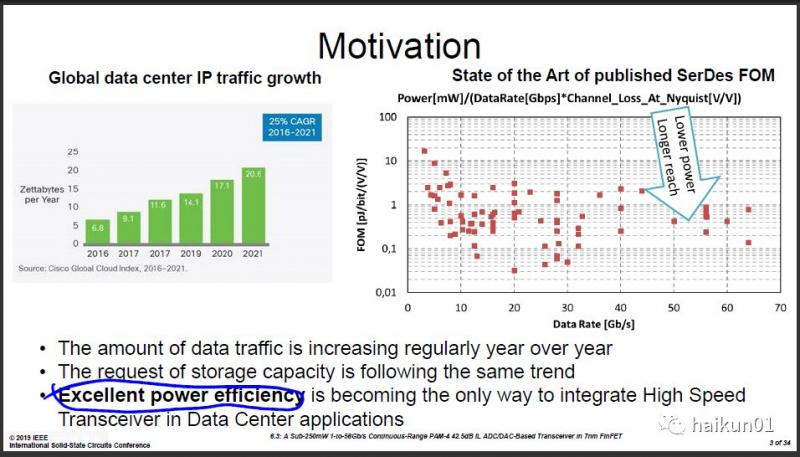

我觉得这种火爆状态会持续好几年。预测是否能保持火爆可以看两方面:一是需求是否在持续增长。这点无容置疑,现在的5G、AI芯片、数据中心、大型交换机都需要传输大量的数据,有数据传输的地方就需要高速串口。高速接口芯片作为基本的数据接口,在一个大系统里必不可少,且不与5G、AI等热点技术构成竞争关系,反而受到这些技术发展的带动。二是现有的技术是否已经能够满足多年内的需求。目前来看,现在的高速接口芯片还没有达到这一点,在能耗和最高的数据率上还有不少提高空间。

从这个session的论文,我们可以看到几点整体发展趋势:

1)尽管56G的市场出货量还没有起来,但业界已经开始了单通道112G的高速接口收发机设计。这是竞争带来的结果,每个公司都尽力往前冲,不进则退,目前并没有看到谁有不可超越的技术优势,那出货时间就显得很重要了。当初我在设计56G的时候觉得,112G速度直接翻了一倍,做起来得有多难,真正做起112G时又觉得难归难,但设计出来还可以。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码