ISSCC 2019论文之引人瞩目的高速接口

编者按:ISSCC会议在集成电路设计的地位无容置疑。ISSCC2019刚刚结束,接下来我将在公众号开启一个新的系列,跟大家一起来读今年的ISSCC论文。今天先来看看第6个session Ultra-High-Speed Wireline都讲了些什么。

2)60Gb/s DSP Based TRX from Huawei Canada

这是一篇来自华为加拿大研究所的文章。

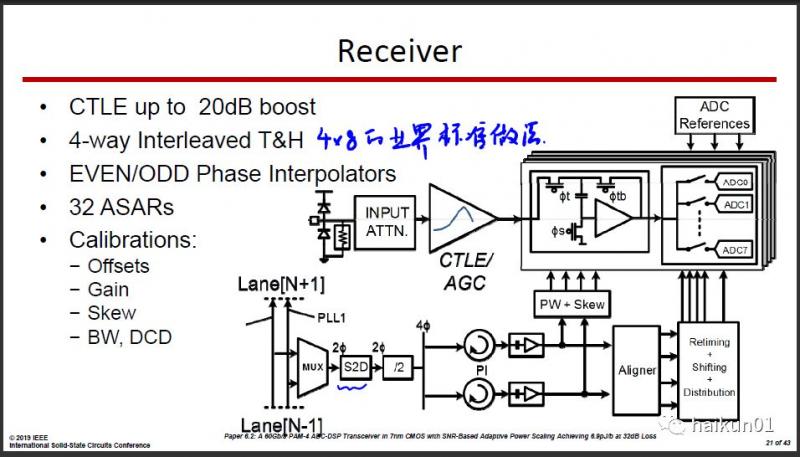

整体采用了较为通用的结构,接收端CTLE接4-路Time Interleaved的ADC,每路Track Hold驱动8个SAR ADC(2-7b可调),这差不多是基于DSP的56Gb/s RX的标准做法了。发射端采用Half Rate,带Phase Interpolator,3个Tap的FFE,这些都是业界常用。

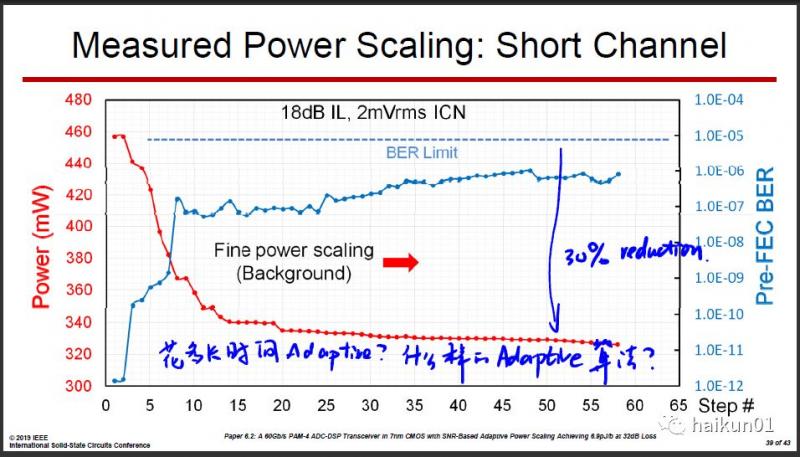

这篇文章的亮点在于芯片上集成了巨多的传感器(温度、工艺、阈值电压等等)、可调电路,理论上可以针对不同的channel、环境和BER要求去优化功耗。去年的ISSCC也有一篇类似的思路,通过改变Flash ADC的位数来调整Power/BER trade-off,感兴趣可以去看看。华为的这篇可调的位置更多,完成度也更高,最后给的测试结果表明通过Adaptive大约可以降低30%的功耗。

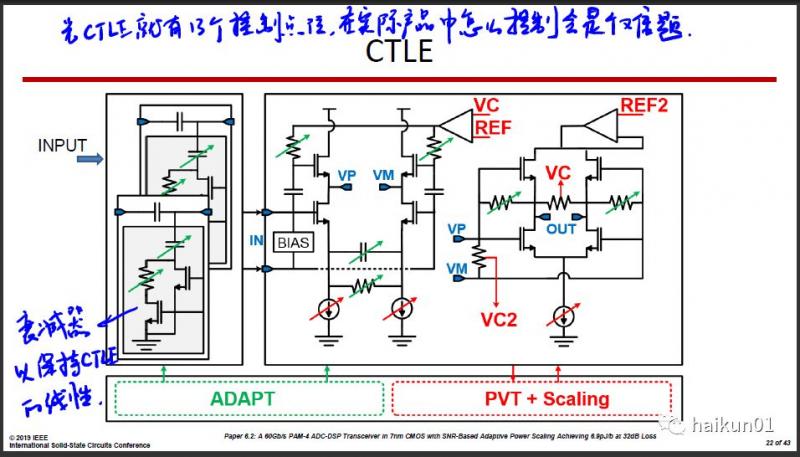

但我有两点疑问。一是成本问题。在模拟电路里,尤其是高速电路,每一个可调都是有成本的,晶体管开关总会引入额外的寄生电容寄生电阻,在这颗芯片里这个成本有多大?相比带来的好处值不值?论文里没有给出具体的数值,因此光看论文很难得出结论。二是Adaptive算法问题。这里面的调节点位实在太多了,而且很多是不相关的,需要处理工艺、温度、channel损耗、BER等等,怎么做Adaptive?这么大的扫描空间,如果暴力扫描,那握手时间太长了,肯定没法用。如果用一些策略,那会不会困在某个局部坏点出不来?如果不能很鲁棒的Adaptive,那实用价值就少了很多。可惜这些数据同样不可能从论文中看到.

还有一点,这篇的全局时钟采用单端反相器来传,应该可以省一些功耗。但似乎这样用的很少,一般都是两根线传差分时钟,理论上对电源地噪声较好,而且对Return Path要求也较低。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码