ISSCC 2019论文之引人瞩目的高速接口

编者按:ISSCC会议在集成电路设计的地位无容置疑。ISSCC2019刚刚结束,接下来我将在公众号开启一个新的系列,跟大家一起来读今年的ISSCC论文。今天先来看看第6个session Ultra-High-Speed Wireline都讲了些什么。

3-4)56Gb/s DSP Based TRX from eSilicon and MediaTek

这两篇论文较为类似,都是采用7nm的DSP Based 56Gb/s Transceiver。他们的结构也是很常用的结构,从论文上来看没有太多可说的。假如现在让我来做一个新的56G系统规划,我也会选这两种结构中的一种。但他们的功耗都做得极为出色,eSilicon的单通道功耗才243mW,MediaTek的只给出了模拟部分的功耗,才180mW,充分展示了这两个公司的设计优化能力。

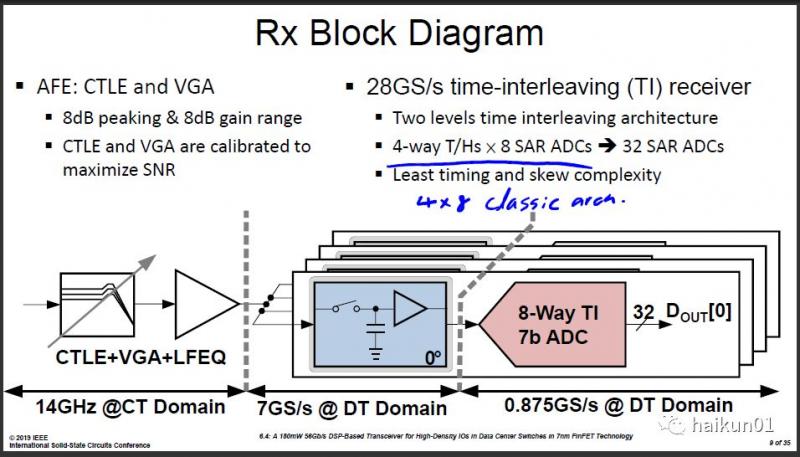

有一点有趣的地方是:MediaTek在RX端使用了4x8(4个Track/Hold,每个驱动8个SAR ADC Slice)的结构,这种是最常见的选择。而eSilicon选择了8x5(8个Track/Hold,每个驱动5个SAR ADC Slice),这样他需要8个相位的8UI时钟,在时钟校准稍微复杂一点,一共8个Track/Hold,对前面CTLE引入的负载电容可能稍大,但每个Track/Hold的尺寸可以较小,每个Track/Hold有较长的时间来充放电。

最终哪一种结构较好?我可能倾向于4x8。但类似这种问题,似乎很难得到直接的证明。架构的比较取决于太多因素了。我们很少有机会把两种架构都做成芯片,去测他们的性能直接对比。即使一种架构的测试结果稍好,那也有可能是这一组人的优化能力较强,不能直接证明架构的优势。最终只能从架构的演化趋势看出一点端倪。

5)100Gb/s PAM4 TRX from Inphi

又是一篇超过单通道100Gb/s的TRX,而且采用了DSP Based。

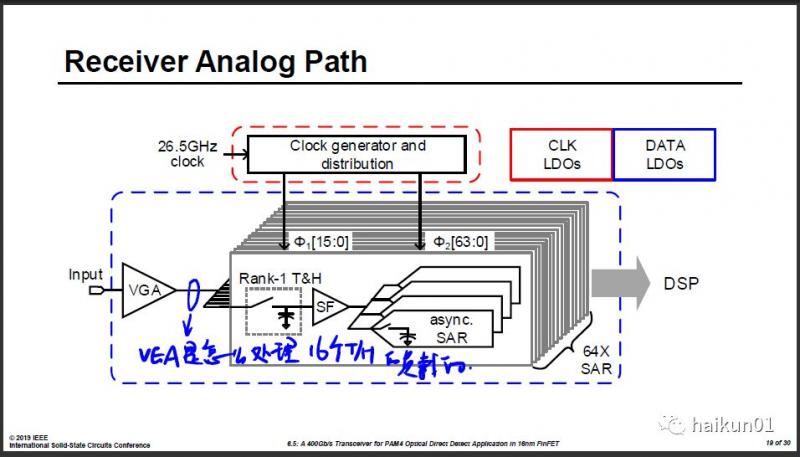

DSP based的100Gb/s的RX难点之一是ADC怎么选。56Gb/s常用的是4x8的结构,这样一个Slice的速度差不多875MHz。到了112G,Slice本身的速度很难翻一倍,那只能采用空间换时间的策略,用更多路的time interleaved ADC来达到整体更高的速度。那么总共需要64个slice,这64个slice怎么分配呢,8x8还是16x4?这么大的寄生电容怎么来驱动?是一个超大的Buffer一起驱动这8个Track/Hold,还是分两级?去年xilinx的112G RX论文就是一个大buffer驱动4个第二级buffer,然后每一个在驱动两个Track/Hold。最终哪一种结构会胜出成为主流,现在还很难讲。因为现在能做出112G的还太少了。

这篇inphi的论文在RX端选择了16x4的结构,这样VGA需要推动16个Track/Hold,而且从他的图中VGA还没有用电感拓展带宽,我不知道他是怎么神奇的做出这么宽带宽的。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码