基于EDA的数据传输系统的HDB3编码器

3 HDB3编码器的仿真

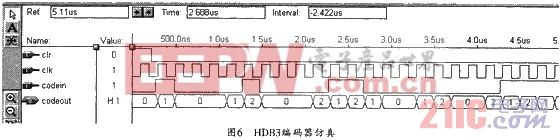

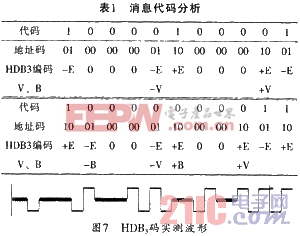

在此,以四连“0”的可能性通过如表1所列的多“0”消息代码进行分析,并利用EDA工具对VHDL源程序进行编译、适配、优化、逻辑综合与仿真。仿真结果显示其完全可以达到编码要求。其仿真图如图6所示。而将HDB3编码硬件描述下载到CPLD或FPGA目标芯片中,然后连接好CC4052进行实际应用测试(用示波器测得)的编码波形如图7所示。

4 结束语

将基于VHDL的HDB3编码用在光纤通信系统中作为误码仪测试误码的HDB3转换器,能满足实际测试的需要。且运用基于VHDL的可编程芯片开发技术将相关的信号处理电路进行硬件描述,并用CPLD/FPGA技术实现数字通信系统,不仅可以实现多种数字逻辑功能,而且可大大提高工作效率,减少电路设计的时间和可能发生的错误,同时也可降低开发成本。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码