基于EDA的数据传输系统的HDB3编码器

2.2 插“B”模块的实现

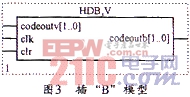

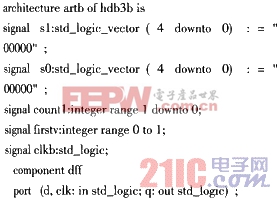

插“B”模块的建模思路是当相邻“V”符号之间有偶数个非0符号时,把后一小段的第1个“0”变换成一个“B”符号。可用一个4位的移位寄存器来实现延迟,这样经插“V”处理过的码元,可在同步时钟的作用下同时进行是否插“B”的判决,等到码元从移位寄存器里出来的时候,就可以决定是应该变换成“B”符号,还是照原码输出。输出端用“11”表示符号“V”,“01”表示“1”码, “00”表示“0”码,“10”表示符号“B”。其模型如图3所示,VHDL的结构代码如artb:

2.3 单极性变双极性的实现

根据编码规则, “B”符号的极性与前一非零符号相反,“V”极性符号与前一非零符号一致。因此,可对“V”单独进行极性变换(“V”已经由“11”标识,相邻“V”的极性是正负交替的),余下的“1”和“B”看成一体进行正负交替,从而完成HDB3的编码。

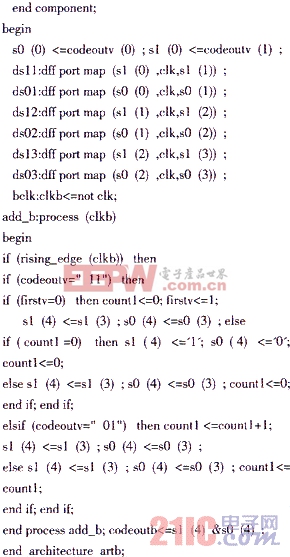

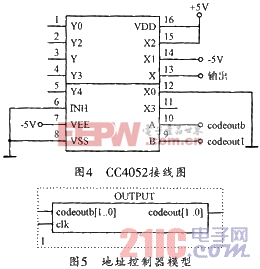

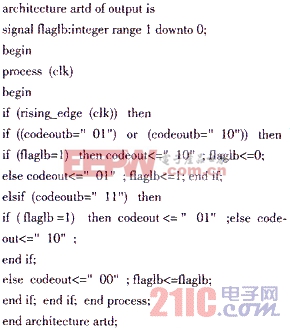

因为经过插“B”模块后, “V”、 “B”、“1”已经分别用双相码“11”、 “10”、 “01”标识。“0”用“00”标识。而在实际应用中,CPLD或FPGA端口的输出电压只有正极性电压,且在波形仿真中也只有“+1”和“0”,而无法识别“-1”。所以要得到所需HDB3编码的结果,需定义“00”、“01”、“10”来分别表示“0”、 “-1”、 “+1”。可将插“B”模块后输出的“00”、“01”、“10”、“11”组合转换为“00”、“01”、 “10”组合,再通过“00”、 “01”、“10”控制四选一数字开关的地址来选择输出通道,就可以实现0、-B、+B。本设计使用CC4052的一组通道作为四选一数字开关,从而将CPLD或FPGA目标芯片的标识性输出转换成双极性信号,最终实现HDB3非归零编码。CC4052的接线如图4所示,所实现的地址控制器的模型如图5所示。其VHDL结构代码如artd:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码