基于EDA的数据传输系统的HDB3编码器

0 引言

数字基带信号的传输是数字通信系统的重要组成部分。在数字通信中,有些场合可不经过载波调制和解调过程,而对基带信号进行直接传输。采用AMI码的信号交替反转,有可能出现四连零现象,这不利于接收端的定时信号提取。而HDB3码因其无直流成份、低频成份少和连0个数最多不超过三个等特点,而对定时信号的恢复十分有利,并已成为CCITT协会推荐使用的基带传输码型之一。为此,本文利用VHDL语言对数据传输系统中的HDB3编码器进行了设计。

1 HDB3码的编码规则

HDB3码是AMI码的改进型,称为三阶高密度双极性码,它克服了AMI码的长连0串现象。

HDB3码的编码规则为先检查消息代码(二进制)的连0串,若没有4个或4个以上连0串,则按照AMI码的编码规则对消息代码进行编码;若出现4个或4个以上连0串,则将每4个连0小段的第4个0变换成与前一非0符号(+1或-1)同极性的V符号,同时保证相邻V符号的极性交替(即+1记为+V,-1记为-V);接着检查相邻V符号间非0符号的个数是否为偶数,若为偶,则将当前的V符号的前一非0符号后的第1个0变为+B或-B符号,且B的极性与前一非0符号的极性相反,并使后面的非0符号从V符号开始再交替变化。

2 HDB3编码器的VHDL建模与程序设计

HDB3码的VHDL建模思想是在消息代码的基础上,依据HDB3编码规则进行插人“V”符号和“B”符号的操作,且用2位二进制代码分别表示。最后完成单极性信号变成双极性信号的转换。其编码模型如图1所示。

2.1 插“V”模块的实现

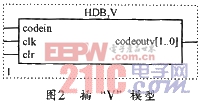

插“V”模块主要是对消息代码里的四连0串的检测,即当出现四个连0串的时候,把第四个“0”变换成符号“V”,用“11”标识。 “1”用“01”标识,“0”用“00”标识。其模型如图2所示,实现的VHDL结构代码如artv:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码