2nm制程:四强争霸,谁是炮灰?

距离 2nm 制程量产还有一年左右的时间,当下,对于台积电、三星和英特尔这三大玩家来说,都进入了试产准备期,新一轮先进制程市场争夺战一触即发。

经过多年的技术积累、发展和追赶,在工艺成熟度和良率方面,三星、英特尔与台积电的差距越来越小了,在 2nm 时代,台积电依然占据优势地位的局面可以预见,但与 5nm 和 3nm 时期相比,市场竞争恐怕会激烈得多。

三大玩家的 2nm 技术路线

在发展 2nm 制程技术方面,台积电、三星和英特尔既有相同点,也有不同之处,总体来看,台积电相对稳健,英特尔相对激进,三星则处于居中位置。

首先看台积电。

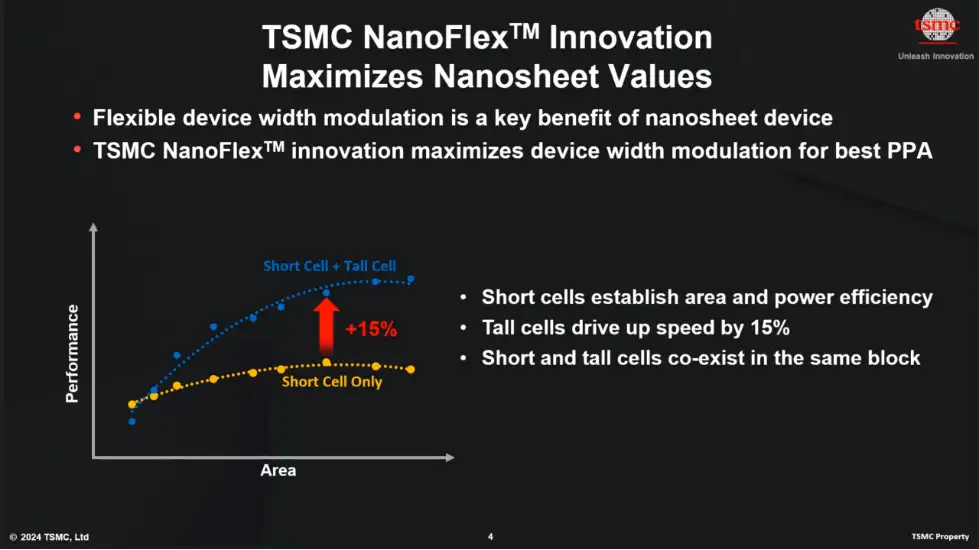

该晶圆代工龙头的 2nm 制程将包括 N2、N2P 和 N2X 三个版本,预计 2025 下半年开始量产其第一代 GAAFET N2 节点芯片,2nm 的下一个版本 N2P 将在 2026 年底量产。与英特尔不同,台积电的这两个版本 2nm 工艺没有使用背面供电技术,不过,整个 N2 系列将增加台积电新的 NanoFlex 功能,该功能允许芯片设计人员在同一模块中匹配来自不同库(高性能、低功耗、不同面积)的单元,以提高性能或降低功耗。

为了控制成本,台积电将使用 GAAFET 晶体管架构,而不是传说中的互补式场效应晶体管(CFET)。

台积电的 3nm 工艺已经支持一种称为 FinFlex 的功能,它也允许设计人员使用来自不同库的单元,不过,N2 依赖于 GAAFET 纳米片晶体管,使 NanoFlex 提供了一些额外的控制能力,可以优化性能和功率的通道宽度。

与 N3E 相比,台积电预计 N2 在相同功率下可将性能提高 10%~15%,或在相同频率和复杂性下将功耗降低 25%~30%。

N2 之后将是性能增强型 N2P,以及 2026 年的电压增强型 N2X。尽管台积电曾表示 N2P 将在 2026 年增加背面供电网络(BSPDN),但看起来情况并非如此,N2P 将使用常规供电电路,具体原因尚不清楚。

N2 仍有望采用与电源相关的创新,也就是超高性能金属绝缘体金属(SHPMIM)电容器,这种电容器可以提高电源稳定性,SHPMIM 电容器的容量密度是台积电现有超高密度金属绝缘体金属(SHDMIM)电容器的两倍多。

下面看三星。

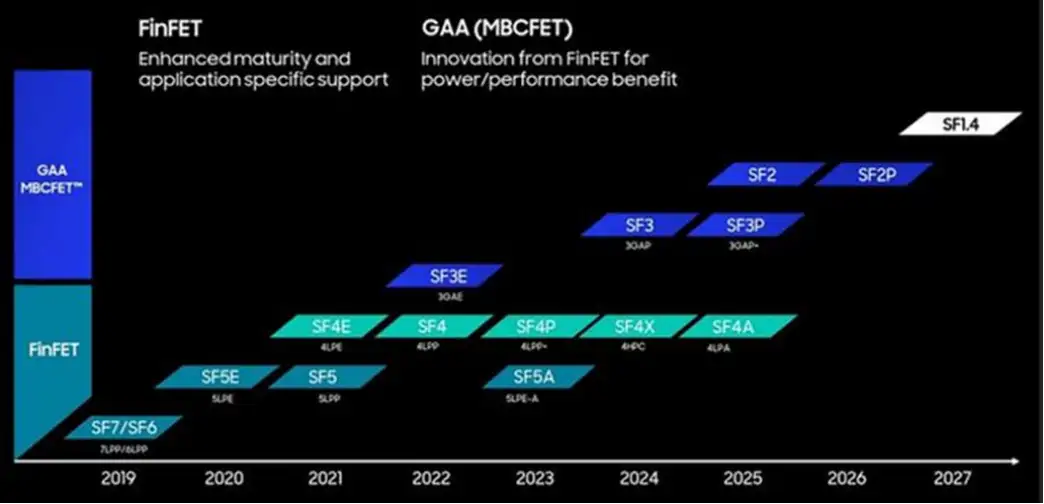

三星也将于 2025 年量产 2nm(SF2)制程芯片,然后于 2026 年采用背面供电技术。与 3nm 工艺(SF3)相比,三星的 2nm 工艺性能提升 12%,功率效率提升 25%,面积减少 5%。

相对于台积电而言,三星公布的 2nm 制程工艺技术细节不多,不知道量产时是否会有什么大招放出。

最后看英特尔。

2024 年初,在发布其「四年内五个节点」计划(称为「5N4Y」)时,英特尔介绍了其 20A(2nm 级)制程技术,该工艺计划在 2025 年初投入生产。

据悉,英特尔的 20A 引入了 RibbonFET GAA 晶体管和 PowerVia 背面供电技术,而之后的升级版本 18A 则将改进这两种技术。该公司是背面供电技术的积极倡导者,并在不断改进,因此,预计英特尔也将会在 2nm 制程技术领域有较多创新。

英特尔将比台积电早两年使用背面供电技术,此外,在使用 GAA 晶体管架构方面,也比台积电早一年半的时间。但是,是否可以将这些新技术转化成实实在在的量产优势,关键还是要看英特尔能否将 PPA(性能、功耗、面积)优化到位。

数字游戏

2024 年 3 月,三星电子通知客户和合作伙伴,宣布将新版第二代 3nm 工艺改名为 2nm。三星称,该工艺将在今年年底量产。

一位 IC 设计业内人士表示:「我们收到了三星电子的通知,他们正在将第二代 3nm 制程更名为 2nm。我们去年与三星电子代工厂签订的第二代 3nm 制程合同也将更名为 2nm,因此,我们需要在不久的将来重写合同。」

有业内人士表示,三星第二代 3nm 制程减小了晶体管尺寸,很大程度上是为了满足营销的需要。

台积电在 IEEE 国际电子元件会议(IEDM)上揭露,将继 2nm 后,推出 1.4nm 制程,且延续将 2nm 正式命名为 A20 的做法,1.4nm 被命名为 A14,预计 2027~2028 年量产。

三星紧追台积电不放,宣布计划 2027 年量产 1.4nm 制程。

英特尔对制程的命名则一改多年前的「倔强」,不再固守摩尔定律的绝对规范,而是考虑到更多的商业化拓展需求,让制程节点听起来更接近市场和客户习惯。因此,该公司 CEO 基辛格在主持英特尔创新日台北场时重申,Intel 7 已进入量产阶段,Intel 4 现已量产准备就绪,Intel 3 也会按计划于今年底推出。他在现场展示了以 Intel 20A 试产出的晶圆,预计将用于 2025 年推出的 Arrow Lake 处理器,Intel 18A 也将有望在 2025 下半年进入量产阶段。

目前,对于 5nm 及以下的先进制程工艺,出现了越来越多的「数字游戏」,这也是竞争压力下的产物,由于台积电的先进制程在业内深入人心,要想提升竞争力,获得更多市场份额,就不得不顺应市场需求和客户习惯,才有助于拓展市场空间。

2nm 制程量产的挑战

2025 年是 2nm 制程量产元年,真正的较量恐怕会出现在 2026 年。对于台积电、三星、英特尔,以及日本的 Rapidus 来说,依然需要解决各自的问题,才能将量产工作铺开。

台积电的高成本

International Business Strategies(IBS)的分析师认为,与 3nm 处理器相比,2nm 芯片成本将增长约 50%。

IBS 估计,一个产能约为每月 50000 片晶圆(WSPM)的 2nm 产线的成本约为 280 亿美元,而具有类似产能的 3nm 产线的成本约为 200 亿美元。增加的成本,很大一部分来自于 EUV 光刻设备数量的增加,这将大大增加每片晶圆和每个芯片的生产成本,而能够接受如此高成本芯片的厂商,只有苹果、AMD、英伟达和高通等少数几家。

IBS 估计,2025~2026 年,使用台积电 N2 工艺加工单个 12 英寸晶圆将花费苹果约 30000 美元,而基于 N3 工艺的晶圆成本约为 20000 美元。

随着对 AI 处理器需求的增加,英伟达在台积电收入中的份额会在 2024 年增加,该公司已经预订了台积电晶圆代工和 CoWoS 封装产能,以确保其用于 AI 的优质处理器的稳定供应。今年,AMD 在台积电总营收中的份额有望超过 10%。

正是有苹果、英伟达、AMD 等大客户下单,台积电才会大规模投资最先进制程,否则,像 2nm 这样烧钱的制程产线,是很难持续支撑下去的。但是,就目前的情况来看,台积电对 2024 全年的晶圆代工市场预判较为保守,认为之前的预估过于乐观了,之前预估该行业年增长 20% 左右,现在看来,增长率可能只有 10% 左右。在这种情况下,虽然有大客户的订单,也必须控制一下成本和资本支出了。

目前,台积电正在全方位的控制成本,包括 EUV 设备的支出,电能的节省等。虽然在 2nm 制程成本方面,其它几家厂商也会面临成本问题,但为了追赶台积电,三星和英特尔似乎在成本方面没有台积电那么敏感。另外,由于台积电要在美国新建至少两座先进制程晶圆厂,这给它带来了很多额外的成本压力。因此,台积电的 2nm 制程产线必须精打细算。

三星的良率问题

对于晶圆代工来说,良率非常重要,它直接影响生产成本和客户认可度。

自从进入 5nm 制程时代以来,良率一直是三星晶圆代工业务所面对的最大问题,特别是在 3nm 制程节点上,三星率先引入了全新的 GAA 架构晶体管,与以往使用的 FinFET 晶体管有较大区别,也使良率问题进一步放大。

据 Notebookcheck 报道,三星的 3nm 工艺良率在 50% 附近徘徊,依然有一些问题需要解决。三星 2023 年曾表示,其 3nm 工艺量产后的良率已达到 60% 以上,不过,现在看来,当时过于乐观了。

今年 2 月,据韩媒报道,三星新版 3nm 工艺存在重大问题,试产芯片均存在缺陷,良率为 0%。报道指出,采用 3nm 工艺的 Exynos 2500 芯片因缺陷未能通过质量测试,导致后续 Galaxy Watch 7 的芯片组也无法量产。报道指出,由于 Exynos 2500 芯片试产失败,三星推迟了大规模生产,目前,尚不清楚是否能够及时解决良率问题。

为了追赶台积电,三星的 3nm 制程工艺采取了比较激进的策略,主要体现在 GAA 晶体管架构上,台积电的 3nm 依然采用 FinFET。2nm 才会转向 GAA 晶体管,激进的结果就是要在良率方面付出一些代价。

如果 3nm 的良率问题不能解决,2nm 恐怕会出现同样的问题。

英特尔的客户

对于晶圆代工业新进入者,英特尔面临的最大问题当然是客户认可度,特别是像 2nm 这样先进的制程工艺,对于在 10nm 以下晶圆代工市场鲜有量产经验和出货量的厂商来说,在与台积电和三星的竞争中,如何抢夺客户,特别是有较大出货量需求的客户(2nm 成本很高,若出货量小,根本不可能盈利),是一大挑战。

Rapidus 的挑战

日本 Rapidus 晶圆厂的 2nm 制程工艺源自 IBM。Rapidus 派遣工程师前往 IBM 在纽约的奥尔巴尼纳米技术中心进行研发,并与 IBM 以外的合作伙伴合作开发 2nm 工艺,目标是在 2020 年代后期进行大规模生产。

与英特尔类似,Rapidus 是晶圆代工业的新进入者,大规模生产工艺研发是从零开始的,客户认可度是一大挑战。

假设已经投资 Rapidus 的丰田汽车、电装、NTT、IBM 等公司将他们需要的先进制程芯片交由 Rapidus 代工生产,但是,这些厂商能有多少 2nm 制程芯片需求?而将先进制程芯片外包给台积电、三星等晶圆代工厂的客户,如苹果、高通、AMD、英伟达和联发科,才是出货量大户,他们能否选择 Rapidus,关键在于这些大客户能够充分了解并认可 Rapidus 的工艺水平,以及所创造的附加值,如果不能的话,他们很难将订单从台积电和三星那里转出。

另外,仅仅在奥尔巴尼学到了 IBM 的 2nm 工艺,并不意味着可以直接将其应用于 Rupidus 晶圆厂的大规模生产,有很多工程问题需要解决,这不是一朝一夕的事情。

还有一个问题是 Rapidus 能获得多少 EUV 设备,这对 2nm 制程芯片量产至关重要。ASML 在 2022 年的 EUV 光刻设备出货量约为 55 台,2023 年的产能提高到 60 台以上,到 2025 年可达到 90 台左右。但是,随着制程工艺的特征尺寸小越来越小,EUV 光刻的层数会持续增加,其它几家晶圆厂会持续争夺 EUV 设备,Rapidus 能得到多少呢?

结语

据韩媒报道,台积电总裁魏哲家没有出席 23 日在台北举行的台积电 2024 年技术论坛,是因为他前往欧洲秘密访问 ASML 荷兰总部和德国工业激光大厂 TRUMPF。

为了冲刺先进制程晶圆代工,英特尔已成为 ASML 首台最新型 High-NA EUV(高数值孔径 EUV 光刻机)的买家。台积电高层原本表示,其 2nm 和 A16 制程节点并不需要 High-NA EUV,因为它太贵了。但据 BusinessKorea 报道,台积电总裁魏哲家这次秘密飞往荷兰,是与 ASML 商讨 EUV 设备事宜。

虽然魏哲家的访欧行程是保密的,但 ASML 新任 CEO 富凯(Christophe Fouquet)和 TRUMPF 公司 CEO 卡穆勒(Nicola Leibinger-Kammüller)都在社群媒体上曝光了魏哲家到访的消息。富凯直言,ASML 向魏哲家介绍了公司的最新技术与产品,包括 High-NA EUV 设备将如何实现未来半导体的微制程工艺技术。

这可以从一个侧面反映出台积电、英特尔和三星争夺新一代光刻设备的竞争在升温,2nm 及以下先进制程的竞赛已经开打。

关键词: SoC

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码