3D封装技术英特尔有何独到之处

编者按:在半导体领域,3D技术带来的革命更叹为观止,早些年的FinFET和3D NAND只是个开始。从去年12月初英特尔公布新架构路线,到1月初CES 2019上拿出M.2 SSD大小的整台电脑,这样的速度,你不得不更上!

一说到2D或者3D,总是让人想到视觉领域中的效果,然而在半导体领域,3D技术带来的革命更叹为观止,早些年的FinFET和3D NAND只是个开始。从去年12月初英特尔公布新架构路线,到1月初CES 2019上拿出M.2 SSD大小的整台电脑,这样的速度,你不得不更上!

到底是什么决定着产品质的飞越,销量徘徊不前的PC到底路在何方?英特尔在此次CES上给了大家答案和思考。

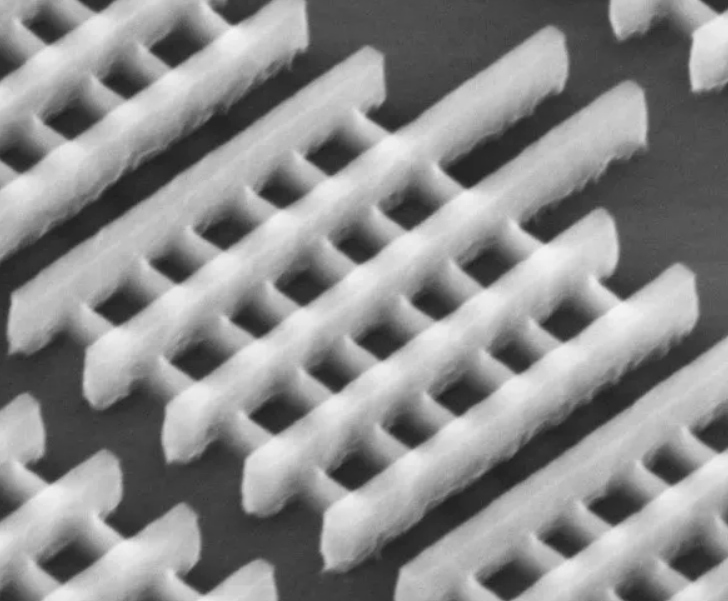

“早”在2011年年中,英特尔推出了向空间要性能的Tri-Gate 3D晶体管技术,成为LSI取代电子管之后,半导体制程革命的新标志。该技术就是今天已经广为各大半导体厂商所采用的FinFET。

从2013年开始,多家主流的Flash厂商开始陆续推出3D NAND产品,最早推出该类产品的三星称之为V-NAND。与该技术普及相伴的是MLC向高堆叠TLC的技术演进,SSD进入寻常百姓家。

在这股浪潮中,英特尔/美光并不是十分积极,直到2015年才少量推出了使用相对独特的浮栅技术的3D NAND产品。真正的大招是他们同时宣布,2017年初正式推出成品的3D XPoint技术,英特尔称之为Optane(傲腾),比单纯的3D NAND只讲求容量增加,更多了一重性能(速度、延迟、寿命)的大幅提升。

可以说,半导体业界近年来每次大的技术飞越,都与3D化——从平面向空间要增长密不可分。而其中,英特尔的角色都是那么的微妙和关键。

刚刚公布就接近产品化的3D封装技术Foveros,将用多么“了不起(Foveros希腊语含义)”的成就改变半导体产业呢?

制程制程,制程是什么?无论是英特尔推演在的14nm、刚刚宣布2019年进入的,还是TSMC于去年下半年开始量产7nm,简单的描述是线宽,是晶片组成的半导体里弄中的道路宽度。路窄不是问题,关键是一方面要能保证车辆正常通行,另一方面还要防止路两侧房间不会隔路“相望”。英特尔不断的14nm制程优化过程,就是路不变窄的情况下,尽可能盖上更多的房间、住下更多的晶体管。同理,7nm的马路虽窄,但若不能很好地隔离不同“房间”间的干扰,房间的实际面积或距离,并不能随同制程改进而缩小,也就是晶体管密度没有增加,一切都等于白搭。

虽然FinFET技术已经完全普及,但是由于大多数CPU或SoC内部结构复杂、同时具有电气性能差异巨大的众多功能模块,FinFET技术只能实现单个晶体管,或者说栅极的空间布局,晶体管本身无法实现多层堆叠,即3D化。在这种情况下,CPU和SoC只能基于单片晶圆生产,同等制程情况下,对应DIE的面积反映出晶体管的数量,间接地呈现芯片性能。这也是摩尔定律已死的理论根源。

3D封装技术,在这里起到了革命性的作用,下面的故事有点像立体种植,把从面积要的产能改为向空间要。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

-

-

-

-

-

-

-

2024-08-01