半导体制造:跟随还是超越摩尔定律

1. 由于氮氧化硅(SiON)栅极介质厚度过薄难以控制,在降低栅极漏电和阈值变异性方面遇到挑战。目前,各大芯片代工厂纷纷转向新的材质和高K金属栅极(HKMG)工艺技术(先栅极和后栅极工艺)。这一变化导致了必须在布线工具和设计规则检查(DRC)工具中纳入新的设计规则。

2. 在193nm光刻基本限值下作业的挑战。设计师必须加强对实施和签核的光刻检查。目前,各个领先的芯片代工厂均要求用户在提交设计前实施某种形式的光刻检查。比如,针对不同Foundry(代工厂)的特点,Synopsys提供不同的工具来协助识别和排除那些导致光刻问题和其它影响良率的设计。

3. 用于参数提取的新工艺拓扑结构建模方面的挑战。目前,各大领先芯片代工厂正创建新的“通孔接触”(via and contact)拓扑结构,来改善芯片的可制造性和维持其密度。STAR RC等提取工具已得到了更新,以更好地了解新的通孔蚀刻效应和凹刻接触技术。

4. 管理参数异变性,尤其是在签核期间异变性的挑战。参数异变性,对比此前工艺节点中的状况,其百分比相对基准数据已出现了显著增长,不过利用最坏情况分析法又过于悲观。目前,芯片代工厂和设计师开始要求采用高级片上变异(AOCV)设计和分析方法,来限定变异性和提供准时的签核。同时要求EDA工具必须具备AOCV分析能力。

与此对应,22/20nm则有不同的要求,EDA工具面临的主要挑战包括以下4点。

1. 新限制性设计规则的增加,以确保利用193nm可成功实现绝对分辨率限值的光刻。为适应这些新规则的要求,必须对布局和布线工具以及DRC检查进行升级。

2. 对于部分层级超越193nm光刻的限值方面的挑战。包括通孔和金属齿距在内的部分芯片层不能在单一光罩内进行投影成像,这是因为这些芯片层在20/22nm工艺下体积太小,密度太大,必须采取双图案模式,将一个单一芯片层的特性分离在两个光罩内。双图案模式提出了新的间距要求,可能增加设计的面积。不过,智能化的布局和布线可以在实际实施时,缓解双图案模式对面积产生的绝大部分影响。

3. 新的提取需求——部分22/20nm工艺增加了凹刻接触等新的结构和拓扑,要求必须具备新的提取能力。

4. 向鳍式场效晶体管(FINFET)/TriGate结构的演进——对整个半导体行业造成了重大影响的英特尔宣布,他们将转向利用TriGate晶体管制造22nm芯片。FINFET/TriGate结构对提取和SPICE模拟具有更高的要求,Synopsys已经开始在EDA工具中考虑这些问题。同时,工艺和设备工程师要在FINFET上开展工艺或设备模拟,也必须拥有从二维TCAD转向三维TCAD能力。

代工厂角度,陈家湘介绍,为了因应全新设计的挑战,TSMC与fabless(无晶圆半导体)客户应该更早、更深入及更紧密的合作,结合双方的优势共同因应未来在设计与技术上的挑战。首先,foundry与fabless 应更早一步定位产品的设计;其次,双方应该更深入地加强硅IP的合作,共同追求可制造性设计(DFM)与设计规范限制(RDR)等设计工具的一致性,进一步从设计到生产的过程中共同解决问题,提升产品质量。目前,TSMC 28nm设计生态环境已准备就绪,发表包括设计参考流程12.0版(Reference Flow 12.0)、模拟/混合讯号参考流程2.0版(Analog/Mixed Signal Reference Flow 2.0)等多项最新的定制化设计工具,强化既有的开放创新平台设计生态环境,帮助客户更快更好的开发28nm产品。另外,28nm产品已进入量产,客户采用TSMC开放创新平台(Open Innovation Platform)所规划的28nm新产品设计定案(tape out)数量已经超过80个。

现实:成本逐渐成第一难题

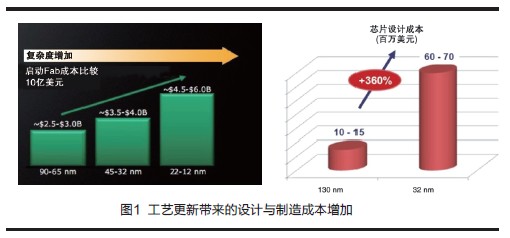

随着半导体工艺向深亚微米发展,半导体设计与制造的成本都呈几何级数增长,以设计为例,32nm的芯片设计成本比起130nm增长了360%,达到了6000万美元,而制造的成本增加更为可怕,新建一条生产线从90nm的25亿美元增加到22nm的超过45亿美元(参见图1)。因此,降低设计生产制造成本,逐渐成为采用先进制程的最大阻碍。

Jean-Marc Chery介绍,若想克服挑战,设计层面最重要的是,技术研发人员与芯片设计、设计工具人员之间必须建立密切的合作关系。制造方面,意法半导体采用和制造技术开发者以及EDA公司紧密合作的方式,以降低自己采用新技术的成本支出,与国际半导体开发联盟(ISDA)的合作就是其中一例。通过与出色的伙伴合作克服上述挑战,为客户提供最佳的解决方案,在成本增加有限的前提下不断提高性能。即将到来的20nm技术节点将使28nm技术节点的系统芯片提高性能30%,并降低制造成本,我们将看到处理速度达到3 GHz的芯片,晶体管数量超过20亿支的裸片,意法半导体将从2012年 (Q1,一季度)开始设计20nm芯片,从 2013 (Q1)年开始提供原型芯片。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码