SOC的高速数据流加密传输的方法实现

处理一个数据包时将整个过程分解为3个部分:接收、加/解密、发送。CPU在每完成一步时仅对这3个模块进行控制,不做数据处理。当大批数据需要处理时,每个时间周期内可同时完成3个数据包中的其中一个步骤,如图2所示,即平均一个时间周期处理一个数据包,该时间周期即为Pipe line周期。但在一个周期内必须保证3个步骤全部执行完毕,CPU才可以对这3个模块进行控制。

由图2可见,Pipe line数据处理周期为:

Tperiod = (Max(Ttx,Trx,Tsec)+Tsys)

在此过程中,如果3个阶段的处理时间相近,处理周期明显减少为原来的1/3左右,一个周期处理一个数据包,速度提高2倍。CPU仅承担控制的任务,并不负责数据的搬运,程序量非常少,这样便大大减少了CPU执行程序所占用的时间。

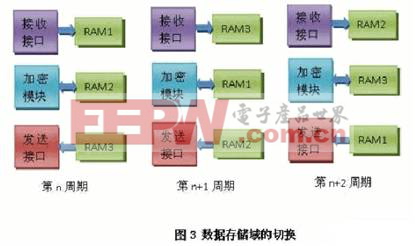

3.数据存储域的切换

如何保证一个处理周期内可同时对3个数据包分别处理呢?本文采用了数据存储域切换的方法。如图3所示,每个功能模块分别对应一个RAM模块,在第n个周期,接收明/密文并存放在RAM1内;在第n+1个周期,将RAM1切换对应到加/解密模块,将RAM1中的数据包加/解密;在第n+2个周期,将RAM1切换对应到发送模块,并将RAM1中的密/明文发送出去,完成同一个数据包的处理过程。

为实现Pipe Line的流水线工作方式,在同一个周期内,同时处理3个数据包。在第n个周期接收数据到RAM1,加/解密RAM2中的数据,并同时将RAM3中的数据发送出去;在第n+1个周期中,RAM1切换到加/解密模块,RAM2切换到发送模块,而RAM3切换到接收模块,这3个功能模块再分别对相应的数据进行处理,以保证平均一个处理周期处理一个数据包,实现pipeline的流水线工作方式。

该实现方法借鉴了CPU执行指令时流水线作业的方式,并使用2个高速的通讯接口,从而保证数据流上的每一时刻每一个模块都在工作。这种方法可以最大限度地利用所有模块资源,大大提高数据流加密的速度,使实时加密通讯和高速加密存储成为可能。

技术亮点

高速数据流加密的实现方法有下面几个技术亮点,可满足实时、高速、安全的需求。

(1)加/解密和数据传输完全由芯片实现,依靠的代码量非常少,硬件实现比软件实现的速度要快十几倍甚至几十倍。

(2)在SOC内部采用Pipe line的流水线架构,使得在同一个周期内并行执行3个模块,同时完成3个任务,大大缩短了一个数据包的平均处理时间。

(3)改变了CPU传统的管理方式,其仅作为加密模块和通讯接口的控制端,而不在数据搬运的通路上,避免因CPU执行冗长的代码时占用过多的时间。

(4)2个高速的通讯接口使接收和发送分开,同一时间可以接收一个数据包并发送另外一个数据包。

(5)内部集成高速的高安全度的加密算法,使数据以密文的形式在通路上出现,保证数据的安全。

通过实际检测并将该方法与传统加密方法进行对比测试,可明显看出采用此方法实现的数据流加密,其速度比传统的方法提高了50倍甚至更高,有效解决了在通讯、移动存储中加入安全度高的加密算法后速度明显降低的问题,为实现高速数据流加密、高安全性的加密存储设备以及安全通讯设备提供了可靠的硬件和技术保障。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码