时域时钟抖动分析(上)

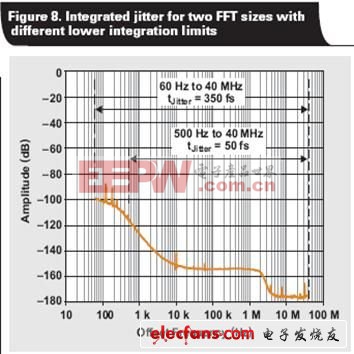

要确定正确的限制,您必须记住采样过程中非常重要的事情是:来自其他尼奎斯特区域的时钟信号伪带内噪声和杂散,正如其出现在输入信号时表现的那样。因此,如果时钟输入的相位噪声不受频带限制,同时没有高频规律性衰减,则整合上限由变压器(如果使用的话)带宽和 ADC 自身的时钟输入设定。一些情况下,时钟输入带宽可以非常大;例如,ADS54RF63 具有 ~2 GHz 的时钟输入带宽,旨在允许高时钟转换速率的高阶谐波。

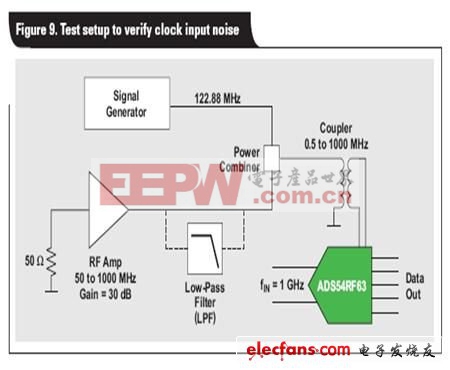

若想要验证时钟相位噪声是否需要整合至时钟输入带宽,则需建立另一个实验。ADS54RF63 再次工作在 122.88 MSPS,其输入信号为 1GHz,以确保 SNR 抖动得到控制。我们利用一个 RF 放大器,生成 50MHz 到 1GHz 的宽带白噪声,并将其添加至采样时钟,如图 9 所示。之后,我们使用几个不同低通滤波器 (LPF) 来限制添加至时钟信号的噪声量。

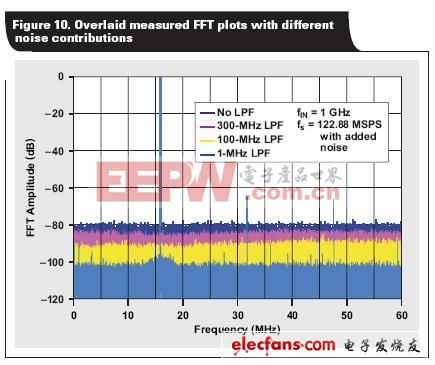

ADS54RF63 的时钟输入带宽为 ~2 GHz,但由于 RF 放大器和变压器都具有 ~1 GHz 的 3-dB带宽,因此有效 3-dB 时钟输入带宽被降低至 ~500 MHz。“表 2”所示测得 SNR 结果证实,就本装置而言,实际时钟输入带宽约为 500MHz。图 10 所示 FFT 对比图进一步证实了 RF 放大器的宽带噪声限制了噪声层,并降低了 SNR。

该实验表明,时钟相位噪声必需非常低或者带宽有限,较为理想的情况是通过一个很窄的带通滤波器。否则,由系统时钟带宽设定的整合上限会极大降低 ADC 的 SNR。

结论

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。“第 2 部分”将会介绍如何使用这种估算方法来推导 ADC 的 SNR,以及所得结果与实际测量结果的对比情况。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码