基于FPGA的24点离散傅里叶变换结构设计

3 仿真验证

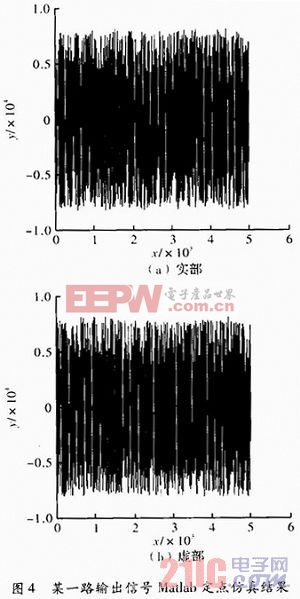

在ISE10.1环境下,采用VHDL完成了24点DFT模块的开发,并采用Modelsim 6.2 b软件进行仿真验证。同时,为验证设计的24点DFT模块的正确性,将Modelsim仿真结果与Maltab定点仿真程序结果进行了对比。输入信号包括24路并行数据信号、1路时钟信号和1路复位信号,输出信号包括24路并行数据信号、1路输出数据有效信号。图4给出了某一路输出信号的Matlab定点仿真结果与Modelsim仿真结果对比图,其中红色表示Modelsim仿真结果数据,蓝色表示Matlab定点仿真结果。从图4可以看出,该路Modelsim仿真结果与Matlab定点仿真结果一样。其他路输出信号Modelsim仿真结果与Matlab定点仿真结果也一样。从而得出设计的DFT模块完全正确。该模块共占用6个Block RAM,14个乘法器,时序仿真结果表明最高工作频率可达200 MHz,该模块已经成功应用于某一数字分路项目。

4 结束语

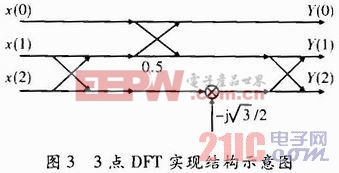

基于Good-Thomas映射算法,并结合ISE10.1软件提供的FFT IP核,提出了一种易于FPGA实现的24点DFT设计结构,设计的24点DFT模块主要由3个8点FFT IP核模块和1个3点DFT模块构成,并且只需要14个实数乘法器。同时,24点DFT模块采用流水线结构,最高工作时钟频率可达200 MHz。该结构还具有良好的扩展性,只需修改FFT IP核模块相应的变换点数参数,就可以实现长度为点的DFT。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码