基于FPGA的24点离散傅里叶变换结构设计

2 基于FPGA的24点DFT设计

为简化设计,假设所设计24点DFT模块输入/输出信号均为24路并行信号。如图1所示,采用Good—Thomas映射算法,可将24点DFT分解成3个8点DFT和8个3点DFT模块构成。由于ISF10.1软件提供的FFT IP核模块输入/输出信号均为串行形式,并且每一个时刻3个8点FFT IP核模块输出的数据恰为1个3点DFT的输入信号。因此,为进一步节约资源,提出一种适合FPGA实现的24点DFT实现结构,如图2所示。相对于图1,改进后的24点DFT只需要3个8点FFT IP核模块和1个3点DFT模块,从而能够大幅节约资源。同时,只需相应修改FFT IP核模块相应参数以及串并转换和并串转换的路数,就可以实现长度为N=3×2n点的DFT。

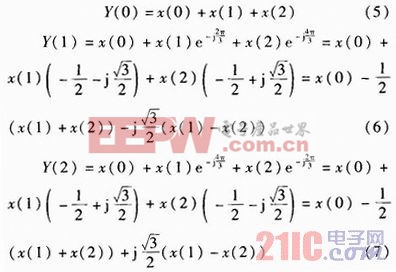

时可以采用两个实数乘法器实现,因此设计的3点DFT仅需要两个实数乘法器,从而节约了乘法器资源。同时,该结构采用流水线操作方式,也提高了实现效率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码