针对FPGA内缺陷成团的电路可靠性设计研究

提高冗余容错电路可靠性策略的定量分析

由于成团因子与冗余容错电路等效面积之间存在复杂非线性关系,无法为上述策略建立分析模型进行定量分析。但当FPGA内只有小于冗余容错电路面积的缺陷团,且成团因子与冗余容错电路等效面积成线性关系,或者可以用线性关系近似时,则可以建立相应的分析模型进行定量分析。

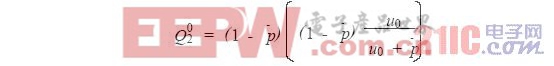

考虑一个单模块单备份容错电路,如图3 所示。A 是主份电路,B 是备份电路。如果单纯考虑信号时延,则布局时应将主、备份电路相邻排列。称这一布局为单模块单备份容错电路的基本布局,基本布局的等效面积为2S0(S0为主份电路面积) ,此时主、备份电路之间的距离为0,对应成团因子为u0,则有基本布局的失效概率Q02为

增大主、备份电路的距离,在主、备份之间留有面积等于m 个主份电路面积的空间。此布局为调整布局。调整布局的等效面积为(m+2)S0 ,此时主、备份电路之间的距离为m ,对应成团因子为um 。

um 和u0有如下关系

调整布局的失效率Qm

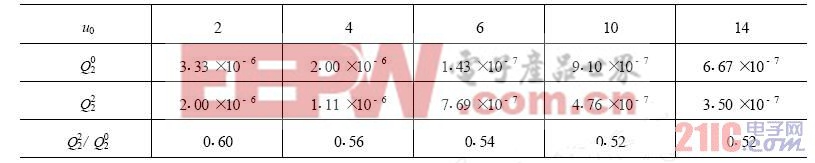

无论成团因子u0取何值,调整布局都能够降低冗余容错电路的失效率。表1 数据反映的是基本布局和特定调整布局(m=2)失效率随成团因子u0的变化情况,主份电路的可靠度p-=0.99999。

在成团因子较宽的一个变化范围内,特定调整布局(m=2)失效率比基本布局失效率降低了约1/2。

表1 失效率随成团因子u0 变化表

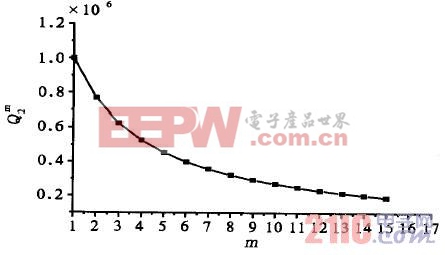

图4 冗余容错电路失效率随距离变化关系

冗余容错电路的主、备份电路间距离越大,冗余容错电路失效率越低。图4是冗余容错电路失效率随主、备份电路之间的距离变化(m变化)的情况,曲线对应的主份电路可靠度p-= 0.99999,成团因子u0=6。

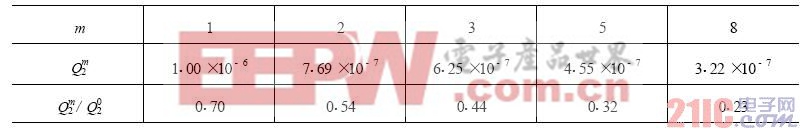

表2 列出了不同布局失效率的具体改善数据,当m=8时,失效率约为基本布局的1/5。

表2 冗余容错电路失效率随布局变化表

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码