针对FPGA内缺陷成团的电路可靠性设计研究

缺陷成团的表象如图1 所示,图中黑点代表缺陷,圆框标注的是一个缺陷团。缺陷团面积是个随机值,大面积缺陷团可以覆盖整个圆晶片,小面积缺陷团局限在一个芯片内,覆盖相邻的若干逻辑块。

缺陷成团使得邻近逻辑块的缺陷存在相关性。要建立反映缺陷成团性的成品率预计模型,需要对复杂的多变量联合概率密度函数积分,可见用解析方法求得成品率几乎是不可能的。因此,通常采用数学逼近的方法,依靠系列可解析函数逼近成品率预计模型。

成品率预计的负二项式分布模型和复合泊松(Poisson) 分布模型,如Neymann TypeA ,Poisson Binomial 分布模型,由于考虑了缺陷的成团性,都能较准确地预计成品率。Stapper等假定p服从B分布,提出成品率复合二项式分布模型,这一模型不仅可以较准确地预计IC成品率,而且便于分析计算。成品率复合二项式分布模型为

式中p-是p的均值,u是B分布的一个参数。

式(3)与式(2)相比,是在式(2)的基础上增加了一个含参数u、p-的比例因子,从而反映出缺陷成团对成品率的影响。

缺陷成团对FPGA片内冗余容错电路可靠性的影响

卫星电子系统的功能电路布局于FPGA内,功能电路由芯片内的若干简单逻辑块构成。为提高功能电路的可靠性,往往需要在片内对功能电路整体采取冗余容错措施,如最常用的单备份冗余容错形式。冗余容错电路包括主份电路、若干备份电路和切换电路,其可靠性是由主份电路、备份电路和切换电路共同决定的。如果主份和备份电路远比切换电路复杂,则可以忽略切换电路对冗余容错电路可靠性的影响,以下的讨论就是针对这一情况进行的。

对于冗余容错电路,不允许主份和备份电路都出现故障,引起冗余容错电路失效。因此有必要采取措施,尽可能降低冗余容错电路的失效率。

无论是FPGA内逻辑单元一类的简单逻辑块,还是处理器阵列中的处理器单元(PE)一类的复杂逻辑块,都可以采用成品率复合二项式分布模型分析其成品率。若把冗余容错电路的主份和备份电路分别看成是片内的一个复杂逻辑块,则可以用此模型分析缺陷成团对冗余容错电路可靠性产生的影响。

复合二项式分布模型的数学推导

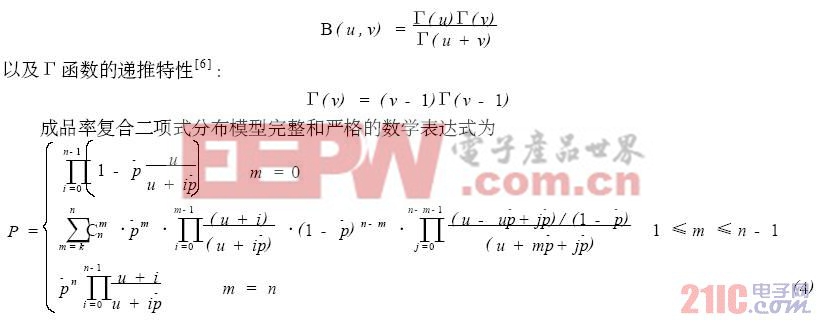

经分析,式(3)给出的成品率复合二项式分布模型表达式存在错误,Stapper在文献中没有给出推导过程,因此首先从数学上对此模型进行了严格推导。推导的关键是利用Γ函数与B函数的关系:

缺陷成团对冗余容错电路可靠性影响分析

式(4)中的第三项对应n冗余容错电路的无故障概率Pn为

式(4) 中的第一项对应n 冗余容错电路的失效率Qn 为

分析式(5) 、(6) ,当参数u 趋近于无穷大时

当参数u 趋近于零时

式(7)、(8)表明,当参数u 趋近于无穷大时,Pn和Qn的值等于缺陷均匀分布时的值,说明此时缺陷不具备成团性,而是呈均匀分布状态; 式(9)、(10)表明,当参数u趋近于零时,Pn和Qn的值分别等于主份电路的可靠度和共效率。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码