L波段直接数字式快跳频率合成器设计

3 L波段快跳频率合成器的实现方法

L波段快跳频率合成器的原理方框如图5所示。主要由晶体振荡器、控制电路、DDS芯片、倍频器,带通滤波器、功率放大器等电路组成。

高稳定度晶体振荡器确保了频率合成频谱的高分辨率以及所需要的跳频速度。设计中我们选用了温度补偿晶体振荡器作为DDS的参考频率源,它具有体积小、功耗低、高频率稳定度和高频谱纯度等特性。

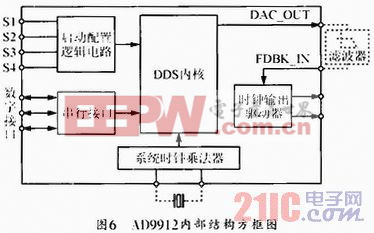

DDS芯片是产生跳频的关键器件,选用了AD公司的AD9912。该器件以其集成度高,功能齐全,性能桌越,设计方便等优点而倍受人们的青睐AD9912内部结构方框图如图6所示。

AD9912电路具有如下特点:

(1)可提供最大1GSPS内部时钟速率;

(2)14位内部集成D/A转换器;

(3)48位频率调节字;

(4)灵活的系统时钟输入,可接受晶振时钟或外部参考时钟。

由于AD9912器件输出功率较低,在送入下级倍频之前须经过放大滤波,得到所需的功率电平和频谱纯度的频率。

倍频部分选用Mini公司的四倍频器,它可将DDS输出的频率倍至我们所需要的L波段,由于它的差损为24~30dB,我们还要使用一级放大滤波,最终得到我们所需的功率电平和频谱纯度的频率放大和滤波电路采用现成集成电路,这样可以减少的调试难度,方便大规模生产,中间加入π型衰减器,用以调整输入输出信号,使它们工作在正常范围。

在完成功能的情况下,电路设计中尽量减少不必要的杂散干扰信号,我们还需要考虑以下几方面问题:

(1)数字电路的抗干扰

数字电路具有系统时钟、高速总线等大功率数字信号,所以它是一个较大的干扰源。对本身杂散就较大的DDS系统来说,解决数字电路部分的干扰是非常重要的。相关的元件尽量放得靠近些使各部件间的引线尽量短。在布局上根据模拟信号部分,数字电路部分,噪声源要分开布局的原则,合理分区布置模拟信号通路,并口输出控制信号以及噪声源器件,减小相互之间的信号耦合。

对于频率源电路,首先元件的性能要稳定,量值要准确,采用优质元件。布线时,电路尽量靠近地,连线要短而粗。如果可能,可以用地线包围振荡电路,晶振电路远离DDS的输出端,两者垂直布线,避免靠近大电流信号线,并且远离发热元件。对于总线的布线,数据线、地址线、控制线尽量缩短,以减小对地分布电容;而且其长短和走线方式尽量一致,以免造成各线阻抗差异过大。如果是双面走线,一定要使两面的线尽量垂直,以防总线间的电磁串扰。同时,对于控制线需要在其上添加对地滤波电容,以及防止线上信号毛刺造成误判。

(2)接地

在高频电路的设计中,应该采用多点接地的方法。电子设备中接地点都直接接到距它最近的接地面上,以使接地的引线最短。这样使得接地线上可能出现的高频驻波现象显著减少。各器件就近接地,就避免了在地线上形成干扰。在整块板上采用多点,大面积就近接地,以缩短电流回路,同时走线中尽量加粗了接地线,以防止接地电位随电流的变化而变化,致使电平不稳,抗噪

声性能下降。

在数模混合的电路中,由于数字部分干扰很多,所以模拟部分易受影响,数字地和模拟地分割开,才能实现数字地和模拟地之间的隔离。

在敏感模拟信号线两边加上保护地,隔离噪声和干扰。

减少输入输出间的串扰、如在DDS、滤波器等器件的输入输出信号间采用了输入输出垂直走线,用地线隔离屏蔽等措施。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码