L波段直接数字式快跳频率合成器设计

其中PLL做锁相倍频,用DDS作参考频率,通过采用高的鉴相频率来提高PLL的转换速度,同时PLL的带通性能可以很好的抑制DDS输出中的部分杂散。这种方案兼顾了DDS和PLL的优点,当环路锁定时,频率合成器的输出频率和频率分辨率分别是:

其中M为锁相环的分频比,K为DDS的频率控制字。

该方案的优点是高分辨率、宽频带、电路结构简单、成本低、易于控制。但由于PLL是倍频式的,因此落在环路带宽内的DDS输出的相噪和杂散将倍增20logNdB(一般取N10),而且该系统的频率转换时间是由PLL决定的,也就是由环路滤波器的带宽决定。所以采用此方案时,要获得优良的相位噪声性能,环路带宽要窄;要获得较快的频率转换速度,环路带宽要足够宽,两者相互矛盾。此外,由于PLL本身固有的延时特性,整个系统的频率转换速度受到限制,最快只能到μs量级。

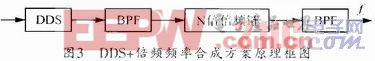

2.2 DDS+倍频频率合成方案

DDS具有超高速输出频率,切换极快以及频率合成器体积小的优势,同时又具有合成频率低的弱点。这样,采用DDS+倍频相结合方式,利用倍频器代替常用的PLL,克服了DDS+PLL频率合成器的频率转换时间较长的缺点。DDS作为频率合成器的核心部分,产生足够多的离散频点,然后用倍频链提高DDS的输出频率,同时拓展了DDS输出带宽最终满足系统要求。DDS+倍频频率合成方案原理框图如图3所示。

该方案可以输出较多的频点、获得较高的频率转换时间、拥有较宽的输出频带以及比较容易实现。但是由于是DDS直接倍频产生的,因此近端杂散较差,而且倍频器也会产生更多的非线性失真和杂散,所以在方案中合理选择DDS输出频段,利用带通滤波器或带通滤波器组有效抑制DDS输出杂散,合理分配倍频器链的倍频次数,可以在保证频率合成器输出频率高速切换的同时达到输出频谱纯度的要求。选择合适的DDS输出频率,可以使DDS本身输出信号杂散最小。足够多的滤波器可以达到满意的频谱纯度。合理的倍频次数可以降低对滤波器的设计要求,将有利于减小输出信号杂散。

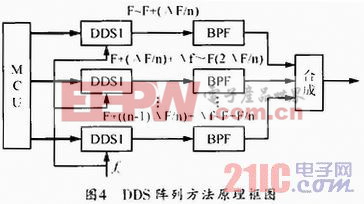

2.3 DDS阵列频率合成方案

杂散抑制是DDS系统设计考虑的主要问题,当DDS输出频带越窄,各种杂散混入其中的几率一般就越小,杂散性能通常就越好。当输出带宽较宽时,如果采用两路或多路DDS并行输出,每一路输出一段频率,然后分别滤波,再通过合成开关输出,从而使宽带频率变成窄带频率。这样可以获得高速高纯度的宽带频率输出。DDS阵列方法原理框图如图4所示。

DDS阵列方法主要缺点是输出频率低,而且由于每路带通滤波器的不理想性会使每路DDS间干扰比较严重。

本文主要是利用DDS技术设计出一个L波段的跳频频率合成器,要求输出频率范围、跳频速度、步进、相位噪声达到一定的技术指标。经过分析,通过以上几种方法的比较,考虑到在实际设计中对频率转换时间有非常严格(几个us)的设计要求,因而使用了DDS+倍频链的组合方案来解决这些问题。这种方案能使设计中最主要的指标——频率转换时间得到保证。

系统性能分析:

(1)若时钟频率为fc,则DDS输出频率fo=(K×fc)/2N,N倍频后系统输出频率为fON=Nfo;

(2)频率合成器输出带宽为DDS输出带宽的N倍;

(3)输出频率分辨率是DDS分辨率的N倍;

(4)系统输出频率切换速率取决于DDS切换速率,达到ns级;

(5)相位噪声

DDS实际上是一个完成分频功能的系统。理论上相位噪声是应陔以分频比N相对于时钟的相位噪声优化20logNdB,但实际上,由于DDS系统内部数字部分又引入了相位抖动,抵消了相噪优化的部分,甚至还使相噪有所恶化。一般情况下DDS输出的相噪要低于时钟相噪,即使参考源的相噪指标再好,DDS系统输出的相噪不可能低于DDS芯片相噪指标的下限。而倍频链完成倍频功能,它的相位噪声相对于时钟的相位噪声恶化20logM(dB),其中M为倍频次数。由此可以看出,使用DDS+倍频相位噪声可按下式计算:Lo=LDDS+L倍(dBc/Hz);

(6)输出杂散

DDS输出频率杂散差的点多发生在其参考源整数分频的时候,可通过DDS输出频率来避开这些杂散大的频点。

通过以上分析可知该方案是满足系统要求的。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码