FAE讲堂:利用赛灵思FGPA实现降采样FIR滤波器

多级方法

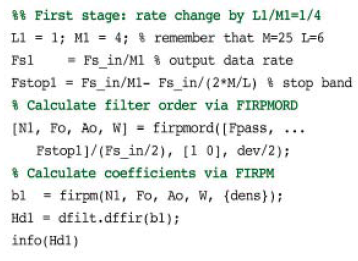

FIR-Complier已经为这种多相L/M=6/25滤波器生成了非常小的内核。不过,我们需要再次采用多级方法,因为这种方

法使我们能够进一步节约DSP48与BRAM。在手动设计多级系统时, 如本例所示,所有滤波级都必须采用与参考滤波器相同的通带频率 (Fpass)。

各级通带纹波均相等,是由参考滤波器通带纹波除以级数算出。各级的差异是阻带频率。第一级无需在Fstop截止,因

为转换带宽会变得太急促(太多系数);现实中我们所需要的只是让第一级在Fstop1=Fs_in/M1- Fs_in/(2M/L)截止。实际上Fs_in/M1与其所有倍数此时都是放置所有复本的新采样频率,而Fs_in/(2*M1)是Fs_in/M1中第一个复本的带宽的一半。以下是相关MATLAB代码。

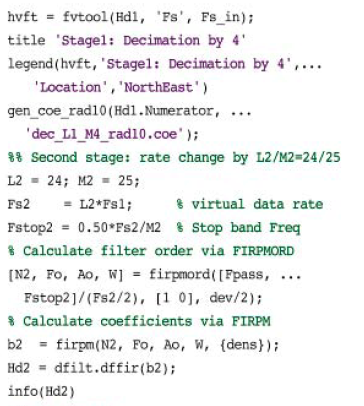

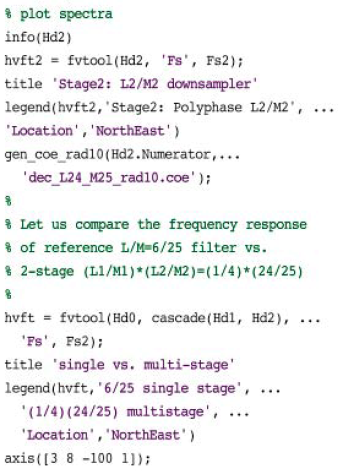

由于第一级是M1=4整数降采样器, 因此其FIRCompiler GUI设置与图1所示非常相似。唯一不同的参数是COE文件名(即dec_L1_M4_rad10.coe)、抽取率值(M1=4)、输入采样频率 (50 MHz) 和时钟频率 (150 MHz)。另一方面,第二级采用 L2/M2=24/25 有理数速率变化,因此,FIR-Compiler设置与图6所示大同小异。此处COE文件名为dec_L24_M25_rad10.coe,插值速率值设为L2=24,而输入采样频率为12.5 MHz。

在布局布线之后,上述两个滤波级占用以下FPGA资源:

第一级(L1/M1= 1/4):

Slice 触发器数量:321 个

Slice LUT数量:223 个

占用 Slice数量:62 个

DSP48 MAC单元数量:4 个

BRAM单元数量:0 个

第二级(L2/M2 = 24/25):

Slice触发器数量:206 个

Slice LUT数量:209 个

占用 Slice数量:68 个

DSP48 MAC单元数量:3 个

BRAM单元数量:1 个

由于采用多级方法,与单级理想滤波器资源占用相比,我们现在可以节约 3% 左右的触发器,4%的LUT,15%的Slice,46%的DSP48以及83%的BRAM单元。尤其是我们只需少得多的MAC与BRAM单元,分别只有6个和5个。原因是第二个滤波器以更低的输入采样频率运行,而采用整数速率变化的第一个滤波器可以充分利用系数对称。

其它资源

我们在本辅导资料中介绍了两个降采样滤波器例子,一个是整数系数(50),另一个是有理数系数(25/6),而且

本文强调了在MATLAB设计滤波器以及采用FIR-Compiler和CIC-Compiler 在赛灵思FGPA中实现它们的方法。相关数据手册详细介绍采用CORE Generator实现滤波器所涉及的参数设置。

如果有兴趣进一步深入DSP领域,有两本专著具体介绍诸多理论和相关 MATLAB 指令:《数字信号处理基础与应

用》,作者:Li Tan(Elsevier,2007 年)和《通信系统多速率信号处理》,作者:Fredric J. Harris(Prentice Hall,2004年)。另外,赛灵思网站提供大量有关多速率数字上变频和下变频的应用手册(尤其是 Xapp113、569、1018 与 936)。

最后,为了理解如何有效实现DSP算法,本人强烈推荐参加赛灵思培训课程《赛灵思FPGA的DSP实现技巧》。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码