FAE讲堂:利用赛灵思FGPA实现降采样FIR滤波器

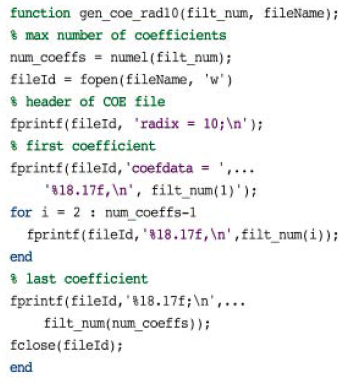

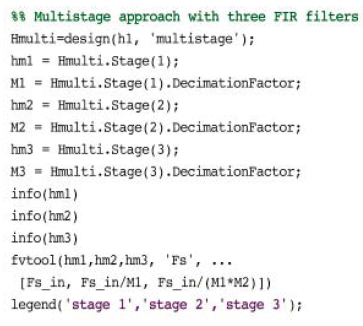

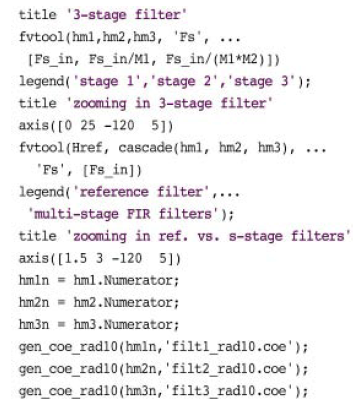

为了设计参考滤波器,CoreGen FIR-Compiler需要名为“COE 文件”的系数文本文件。以下MATLAB例程说明如何以十进制基数轻松生成此 COE 文件;FIR-Compiler 然后按照所采用的设置量化相关系数。

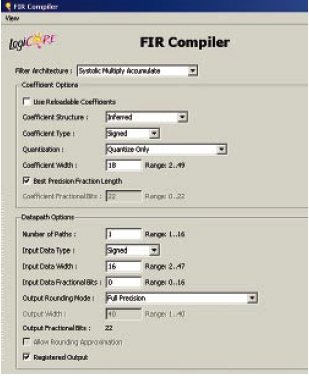

图1与图2说明FIR-Compiler GUI头两个页面所应用的设计参数;在最后两个页面我只需接受其默认值,但是“优化目标 (Optimization Goal)”除外, 我把它设为“速度 (Speed)”而非“区域 (Area)”。如无明确说明,我在本文件以及下面例子中始终采用上述设置。在完成ISE 11.4布局布线之后,参考单级降采样滤波器占用以下FPGA资源:

Slice触发器数量:1,265 个

Slice LUT数量:1,744 个

占用的 Slice数量:502 个

DSP48单元数量:22 个

图 1. 50整数降采样。参考单级滤波器的FIR-Compiler 5.0 GUI设置第1页(共4页)。

图 2. 50整数降采样。参考单级滤波器的FIR-Compiler 5.0 GUI设置第2页(共4页)。

三个FIR滤波级串联

现在我们以滤波级串联方式实现理想抽取滤波器。这种方法可以让我们通过时分复用节省MAC单元,因为每个新的滤波级都是按前一级提供的较低数据速率运行。我让FDA工具决定最佳滤波类型:利用 MATLAB 指令信息,您可以看出:它会提出三级解决方案建议,其抽取因数分别是M1=2、M2=5和M3=5。

图3显示了组成上述多级系统的三个滤波器的频率响应。蓝色曲线代表第一个降采样滤波器(M1=2);绿色曲线代表第二个滤波器 (M2=5),按Fs_in/M1倍数周期波动;而红色曲线则代表第三个降采样器 (M3=5),按Fs_in/(M1*M2)倍数周期波动。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码