xilinx FPGA中oddr,idelay的用法详解

我们知道xilinx FPGA的selectio中有ilogic和ologic资源,可以实现iddr/oddr,idelay和odelay等功能。刚入门时可能对xilinx的原语不太熟练,在vivado的tools-> language templates中搜索iddr idelay等关键词,可以看到A7等器件下原语模板。复制出来照葫芦画瓢,再仿真一下基本就能学会怎么用了。

1. oddr

oddr和iddr都一样,以oddr为例,先去templates里把模板复制出来。

Add simulation source,建立一个简单的仿真文件。

module simu_oddr(

);

reg clk = 1'd0;

always

forever #2 clk = ~ clk;

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(clk), // 1-bit clock input

.CE(1'd1), // 1-bit clock enable input

.D1(1'd1), // 1-bit data input (positive edge)

.D2(1'd0), // 1-bit data input (negative edge)

.R(1'd0), // 1-bit reset

.S(1'd0) // 1-bit set

);

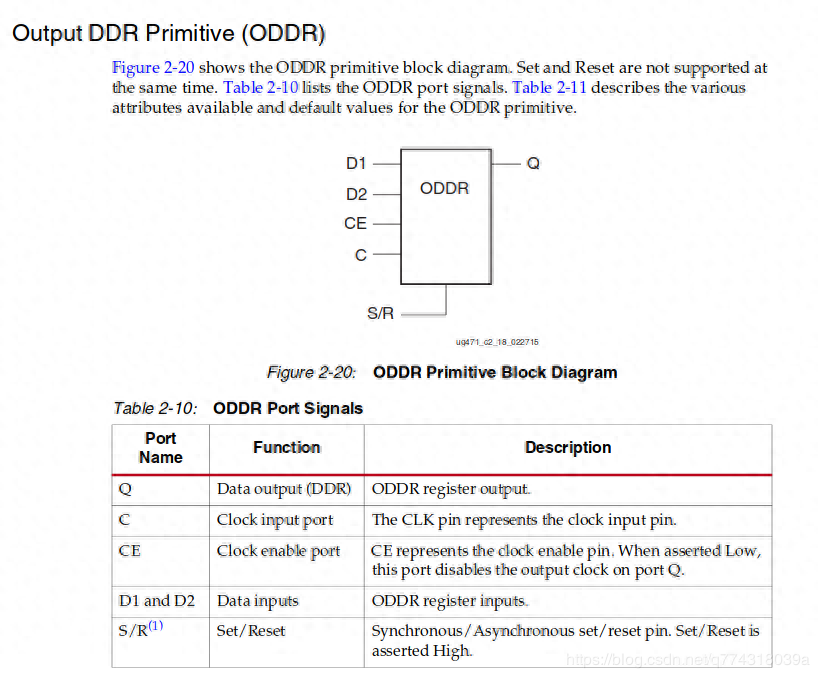

endmoduleODDR的使用方法在selectoi中的参考手册ug471中127页开始有说明,使用这些资源首先要参考的都是官方的资源手册。

简单说明:

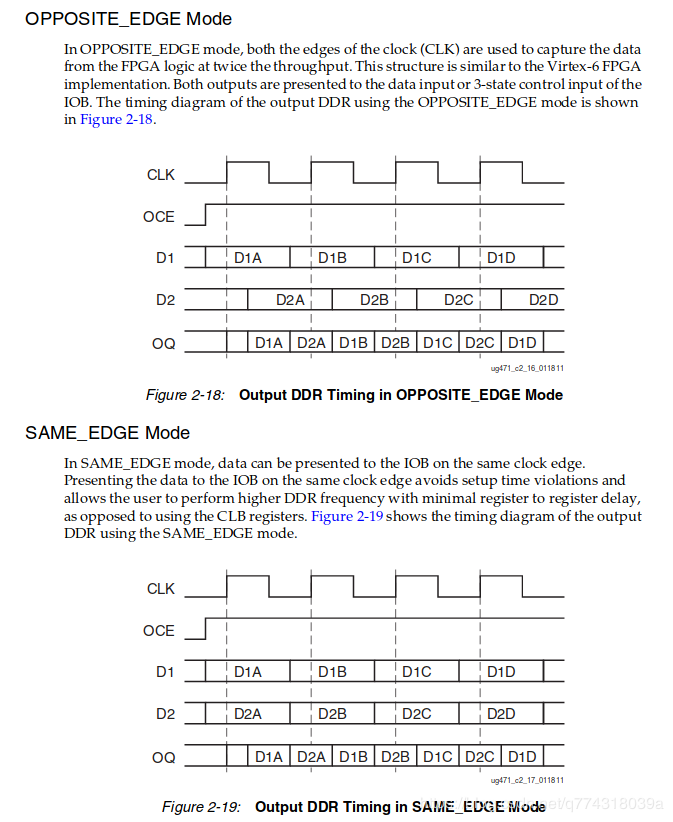

CE是使能,C是时钟,在时钟的上升沿下降沿分别输出D1和D2,Q是输出,S/R是复位,R = 1 Q输出0,S= 1,Q输出1,默认情况应该两个都等于0 ,两个都等于1时,输出0。"OPPOSITE_EDGE" or "SAME_EDGE" 手册中也有说明,指明采样时刻不同,具体有什么应用上区别我也不知道。

通过仿真,就可以看到输出是什么情况,在上升沿输出1,下降沿输出0,还可以看到输出有一点滞后。iddr和oddr在rgmii的接口中就可以方便地接收数据,转为gmii。一般情况要注意下时钟和数据的对齐问题,采样时钟可以相位往后一点,90° 1//4周期,输出的时候时钟也相应地滞后一点,就根据实际情况来,125M的DDR还是很容易采样稳定的。

2.idelay

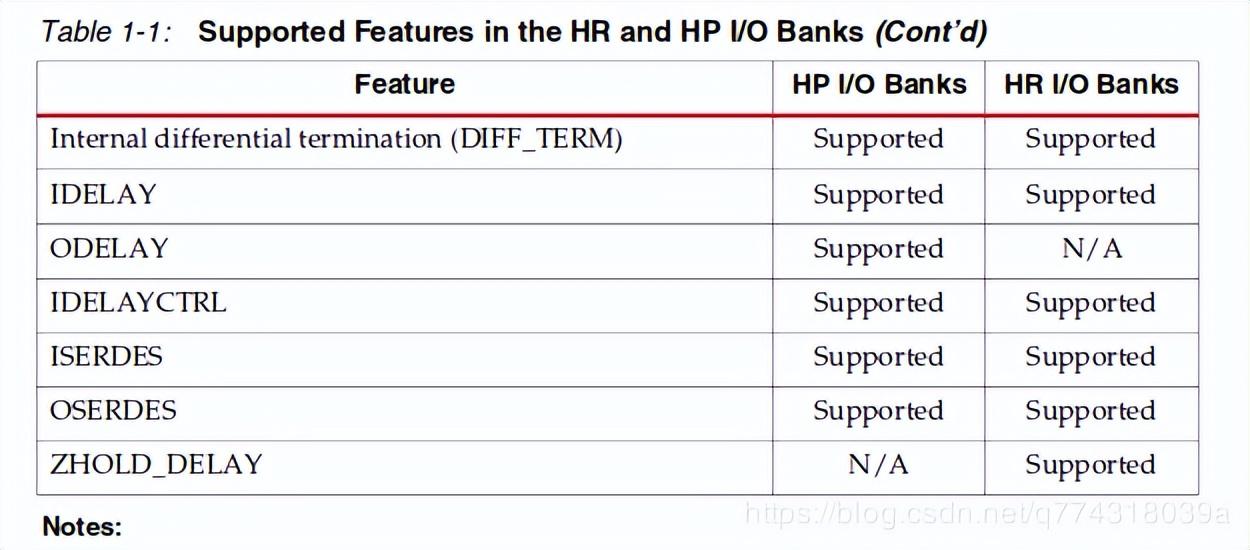

在ug471告诉我们,只有hp bank才有odelay,在ug475中说明哪些系列有hp bank,简单说hp bank速度快很多,支持odelay,电压只能1.2V- 1.8V。其中A7全系是没有odelay的,K7才有(保留意见,简单看了一下),所以在language templates中搜索odelay是没有A系列的原语的。

idelay作用就是实现输入延迟,实际中应该有更明确的用法,这里只是我自己学习时的一些介绍。同样在ug471中对idelay也有介绍,有固定延时,可变延时,使用时都要例化idelay ctrl,延时的精度就可idelay ctrl的接入时钟有关。一个bank 只有1个idelay ctrl,同一个bank 要用idelay或者odelay,延时精度是一样的,虽然可以idelay ctrl可以接200Mhz,300Mhz,但同一个bank只能接1个,也只需要例化一次。多个bank要用idelay时,就要例化多次。

`timescale 1ns / 1ps

module s(

);

reg clk = 1'd0;

always

forever #2.5 clk = ~ clk;

(* IODELAY_GROUP = "idelay" *)

IDELAYCTRL IDELAYCTRL_inst (

.RDY(), // 1-bit output: Ready output

.REFCLK(clk), // 1-bit input: Reference clock input

.RST(1'd0) // 1-bit input: Active high reset input

);

reg clk2 = 1'd0;

always @(posedge clk)

clk2 <= ~clk2;

wire DATAOUT;

(* IODELAY_GROUP = "idelay" *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL

IDELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(31), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data output

.C(1'd1), // 1-bit input: Clock input

.CE(1'd0), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(1'd0), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(1'd0), // 5-bit input: Counter value input

.DATAIN(1'd0), // 1-bit input: Internal delay data input

.IDATAIN(clk2), // 1-bit input: Data input from the I/O

.INC(1'd0), // 1-bit input: Increment / Decrement tap delay input

.LD(1'd0), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(1'd0), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(1'd0) // 1-bit input: Active-high reset tap-delay input

);

endmodule这里例化了一个idelay ctrl,是属于idelay group的,这个声明还没有研究过有什么用,不知道是不是指定idelay2和哪个ctrl是绑定的。idelay ctrl端口很简单,仿真时复位rst接0就好了,实际中推荐接输入时钟的pll lock引脚取反,保证在时钟锁定前(lock = 0)idelay ctrl处于复位状态。

idelay2中按推荐配置,从DATAIN还是从IDATAIN输入区别为是内部延时还是从IO输入,FIXED固定延时,idelay value先输入0,,时钟是200M,其他全部接0。此处,idelay的作用就是把IDATAIN的信号接入ilogic中,延时0个tap再从DATAOUT输出。可变延时的使用说明ug471上都有,还没学习,有需要了再去看。

idelay 有0-31个tap,分割200M的半个周期2.5ns,每个tap就是2.5ns/32 = 0.078125 ns

value = 0 可以看到输出延迟了0.6ns,value = 10时,延时了1.38ns。0.078125 * 10 + 0.6 = 1.38125,大体相近的。

其实oddr,idelay这些资源应该用起来都比较简单,可能我实际中就用了一下oddr/iddr,也没有觉得有多少难以调试的地方,本文简单介绍了这2个原语的使用方法,从复制原语,看手册介绍到仿真,其他原语也是类似的,学会如何去学习最重要。

文末再介绍一下generate,一样的在tools -> language templates中搜索。

genvar; generate for (=0;<;=+1) begin: end endgenerate

用这个可以很方便地例化出多个相似的模块。

genvar i; //genvar i;也可以定义到generate语句里面 generate for(i=0;i<10;i=i+1) begin:mymodule assign a[i]=reg[i]; end endgenerate

关键词: xilinx FPGA oddr idelay

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码