支持ONFI同步模式的NAND Flash控制器设计

3 同步模式设计

3.1 同步接口设计

支持ONFI2.0及以上的NAND Flash芯片既支持传统的异步接口模式,也能通过配置工作在源同步的DDR接口模式下,从而达到速度的提高。如图4所示,在同步工作模式下,增加了DQS信号,并将异步模式下的WE#信号变为CLK信号,RE#变为W/R信号。有很多文献介绍了传统异步接口模式下的NAND Flash控制器设计,本文不再赘述,以下开始介绍同步工作模式下的接口电路设计。

当NAND Flash工作于同步接口模式时,接口I/O数据为DDR形式,读写操作时序见图5,可以发现它非常类似于DDR SDRAM的时序,其中DQ[7:0]为数据,DQS为数据选通信号,其基本思想就是将两组持续时间为一个时钟周期的数据合并,使得在传输过程中一个时钟周期的上升沿和下降沿都能传输数据,从而获得传输速度的倍增。

DQ和DQS均为双向驱动信号,当进行写操作时,由控制器进行驱动,当进行读操作时,由Flash芯片内部进行驱动,本文双向信号采用图6方法实现,该结构需要置于整个设计的顶层,从而利于综合的进行。

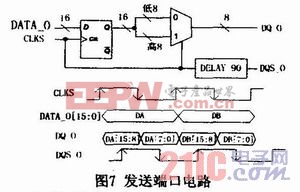

DQ与DQS信号间的相位关系对DDR接口非常重要。当对NAND Flash进行写操作时,控制器必须产生一个与DQ数据信号中心对齐的DQS信号,所用发送端口电路如图7所示,CLKS为同步接口模式下系统的整体时钟。通过多路选择器实现16bit数据DATA_O转两组8bit数据DQ_O输出。CL-KS为高时对应DATA_O的高8bit数据,CLKS为低时对应DATA_O的低8bit数据,最后将CLKS进行移相作为DQS_O选通信号输出。

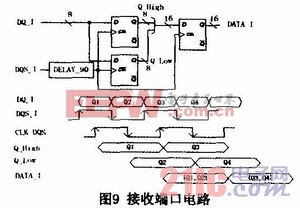

当从Flash存储器件读取的时候,Flash输出的DOS信号是与DQ信号边沿对齐的,需要对接收到的DQS信号进行相移使之与DQ信号中心对齐,以采到准确的数据。图8是DQS移相后与DQ中心对齐的实际仿真波形图。所用读接口结构如图9所示,首先将DQS_I选通信号进行移相,然后通过两组分别为上升沿触发和下降沿触发的寄存器采样与DQS_I上升沿和下降沿对齐的两组8bit数据DQ_I,并通过一组同样是上升沿触发的寄存器将这两组8bit数据合并成16bit数据。

实现读写操作的电路中都使用了DELAY单元,以达到移相的目的,DELAY单元可以由两种方法实现:DLL和延迟线。将相移定为90°,是假设DQ和DQS是理想的源同步接口,并假定DQ和DQS经过芯片内部延时、PCB板上延时及pin脚延时是相同的,这样能得到最理想的数据窗口。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码