多码率QC-LDPC译码器设计与实现

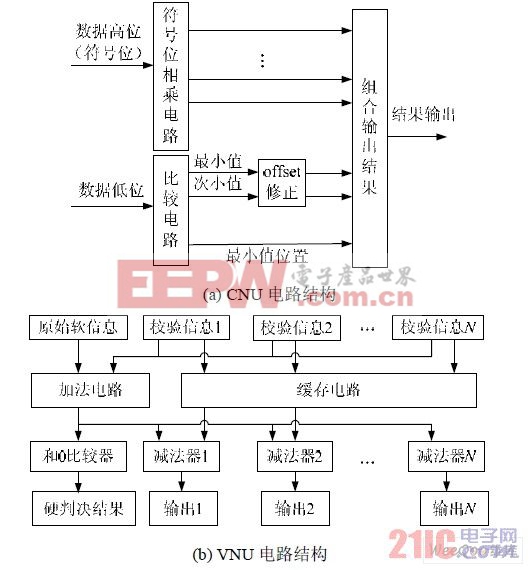

具体结构如图2(b)所示。

图2 CNU 和VNU 电路的结构

输出缓存RAM 组用来存储和输出译码结果,同样也采取了乒乓操作,支持数据块连续的输入输出。控制和寻址模块是译码器的核心模块,它为译码器提供各种控制信号和读写RAM 的寻址信号。寻址模块分为CNU 地址产生模块和VNU 地址产生模块两部分,CNU 地址产生模块的起始地址都是其偏移值;而VNU 地址产生的地址则都是从0 到Z。

由于采用了输入输出双缓冲,所以译码器中最多可以存在三块数据块,同时这三块数据块可以是不同码率的数据块,这就实现了对连续输入的不同码率数据块自适应译码的功能。

4 FPGA 实现以及性能测试:

根据以上设计方案,选用Verilog HDL 进行设计,同时采用了Modelsim 6.1b 进行了仿真验证,最后在STratix IIEP2S180F1020I4 芯片上进行了测试。具体见表1 所示。

表1 资源占用情况

表1 中同时也列出了一个单码率译码器的资源占用(7/8码率)。可以看出,该多码率译码器在资源占用不超过2 种码率译码器资源之和的前提下能够有效支持3 种码率。

同时,还针对每种码率都测试了其吞吐率和运行的最高时钟,其中三种码率(1/2,3/4,7/8)工作最高时钟均为110 MHz,最高吞吐率分别为110 Mb/s、165 Mb/s 和192.5 Mb/s。从该测试结果可以看出,该多码率译码器吞吐率也在110 Mb/s以上,说明其在满足自适应多码率应用需求的同时,仍然保持了很高的译码吞吐率。

5 结语

针对QC-LDPC 码特点,提出了一种多码率QC-LDPC译码器实现方法,并用FPGA实现了此通用的多码率译码器,可支持至少三种不同码型的QC-LDPC 码。此多码率QC-LDPC 译码器的输入输出参数可以根据所需支持的码型灵活配置,最终实现的译码吞吐率对任何码率都可超过110 Mb/s,兼顾了多码率译码器所需的灵活性和高吞吐量。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码