多码率QC-LDPC译码器设计与实现

3 多码率LDPC 译码器设计

首先考虑下面3 种QC-LDPC 码字作为参考,码长8 064bit,码率分别为7/8, 3/4, 1/2。其中,不同码率的最小和译码算法所需的最佳偏移值((3)式中的offset 值)经仿真得到,分别为1, 0.7, 0.5。上述QC-LDPC 码中所用到的码型膨胀因子是112。

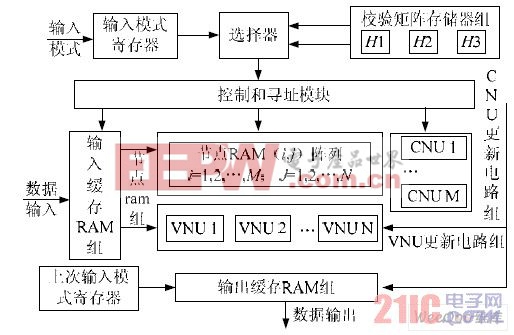

文中实现的LDPC 译码器基于部分并行的译码结构,对译码器进行了输入输出双缓冲处理,支持数据连续处理,总体的结构如图1 所示。

图 1 译码器的总体结构

由于要支持三个不同H 阵的LDPC 码,所以需要有一个模式端口,告知译码器当前数据块是属于哪个码型。输入模式寄存器控制选择器选择不同的H 阵来配置控制和寻址模块,使其能选择需要更新的节点RAM 和需要更新的校验节点单元(CNU),变量节点单元(VNU)的电路套数。

输入数据首先输入到输入缓存RAM 组中,输入缓存RAM 组按照基本矩阵的列数分成N 块对数据进行缓存,其中N 可配置,文中用到的N 是72。数据存满一帧编码块后,就输入到节点RAM 组中。节点RAM 组的作用是对算法迭代更新时的中间信息进行存储。由于基本矩阵中有较多的零矩阵,所以实际生成的节点RAM个数远小于M × N 个。

CNU 电路的用途是做校验节点概率更新,完成式(3)的计算。实现结构如图2(a)所示。VNU 电路的用途是做变量节点概率更新,同时计算硬判决结果,完成式(4)和式(5)的计算。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码