FIR滤波器的FPGA实现方法

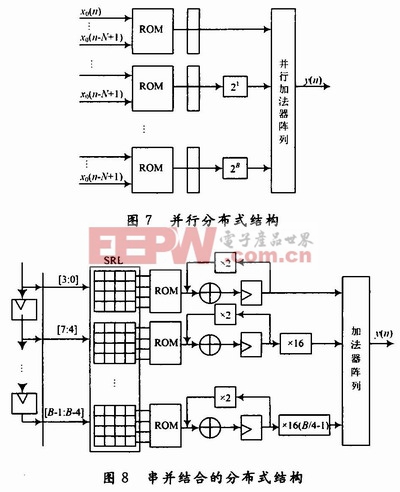

(2)第二种结构为并行分布式结构。并行分布式结构就是将N个输入量的不同位进行同时查表,而相同位送入同一个ROM寻址,不同位有不同的ROM。其结构如图7所示。

第三种结构为串并结合分布式结构。它是一种折中方案,既要求速度不太高又要求资源占用少。对于串行分布式算法,是一次一位(one bit-at-a-time,1BAAT)查找表,而并行分布式算法是一次B位(B bits-at-a-time)。所以串并结合分布式算法采用一次多位,如2BAAT,3BA-AT。图8所示为4BAAT查找表结构图。

图8中位数B是4的倍数,SRL为移位寄存器。SRL中第1行从右边数第1列为数据的0位,第2列为数据的1位,第3列为数据的2位,第4列为数据的3位。类似地,第2行右数第1列为数据的4位,第2列为数据的5位,第3列为数据的6位,第4列为数据的7位。以后各行按相似的数位顺序排列。在第一个时钟周期,数据的0,4,…,B-4位同时进入查找表ROM中,查出所要的数据,第二个时钟周期,1,5,…,B-3位同时进入ROM中,查出所要的数据,所查得的数据传递给下一级累加器进行累加,这样依次对剩下的各数据位进行同样的操作。由于每个块之间相差4位,即16倍,为了对应位相加,所以乘16。FIR滤波器的分布式算法结构比单独用乘法器实现的速度快,特别是滤波阶数越高,其优势更加明显。分布式结构中,串行结构是1次查询1位,所以对B位的数据在不算上移位寄存等的时间,完成1次滤波需要B个时钟周期;而并行结构只需要1个时钟周期便完成滤波,所以并行结构是速度最优的结构,但是并行结构需要B个DA查找表,需要大量的ROM来储存,加大了硬件资源的消耗,特别是阶数越高,硬件规模将十分膨大;串并结构综合两种结构优势,实现在速度和规模上的协调。实际应用中。需根据系统的要求来选择合适的结构。

3 结语

本文定性地分析了各种FIR滤波器的FPGA实现方法。对于低阶的FIR滤波器可采用串行结构、并行结构以及转置型结构来实现,而并行结构和转置型结构的FIR滤波器以牺牲资源损耗来实现了速度上优势;对于高阶的FIR滤波器,基于乘法器结构的串行结构、并行结构及转置型结构在速度上难以达到高速处理的要求,而分布式算法将乘法转换为查表和累加的结构,使得分布式结构的FIR滤波器在速度上得到了提高,

但三种不同形式的分布式结构要在综合考虑资源以及速度的基础上进行合理选择;同样采用FFT实现的FIR滤波器以减少运算量来获得了速度上的提高,特别是滤波阶数越高其速度提升越明显。

现代工程技术领域对滤波系统的带宽、高速、信号的实时性处理等方面要求越来越高,在运用FPGA来实现FIR滤波中,基于乘法器结构的FIR滤波器无法满足以上要求,而分布式结构的FIR滤波器巧妙地运用ROM查找表来实现固定系数的乘累加运算,避免了乘法运算,并且在随后的每级加法运算中引入流水线结构,提高了速度。因此采用分布式算法实现FIR滤波器是目前研究的热点,同时无论哪种分布式算法都要使用ROM来做查找表,但是随着滤波阶数的增加,ROM的数量将会增加,在进一步提高速度的情况下如何减少ROM的数量是今后亟待解决的问题。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码