FIR滤波器的FPGA实现方法

2.3 转置型结构

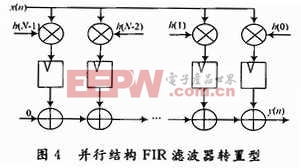

根据转置定理,如果将网络中所有的支路方向倒转,并将输入x(n)和输出y(n)相互交换,则其系统函数H(z)不变。通过转置定理,将并行结构的FIR滤波器变换就可以得到转置型FIR滤波器,其结构如图4所示。

基于并行结构的转置型FIR滤波器实现了数据的并行输入,在1个周期内就能完成1次滤波,并且各级结构相同,在每个阶段都可以读出数据,可以对滤波阶数进行扩展或者缩减,实现任意阶数的滤波器。但是由于基于的是并行结构,便有着并行结构的一些缺点,主要是对于高阶的滤波器,其资源占用量是巨大的,设计成本高。虽然这样,转置型FIR滤波器仍是应用广泛的一种滤波器。

2.4 基于FFT的结构

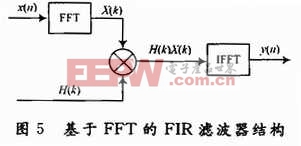

应用快速傅里叶变换(fast fourier transform,FFT)实现FIR滤波器是一种快速实现滤波算法的重要途径。由式(1)可知,FIR滤波器的输出y(n)是输入x(n)与系统冲击响应序列h(n)的卷积,应用FFT可以快速实现卷积变换。如图5所示,先将输入信号x(n)通过FFT变换为它的频谱采样值X(k),然后再与FIR滤波器的频响采样值H(k)相乘,H(k)可事先存放在存储器中,最后再将乘积X(k)H(k)通过快速傅里叶反变换(IF-FT)还原为时域序列,即得到输出y(n)。

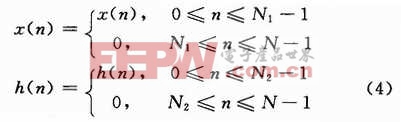

为实现FFT,根据两有限长序列的线性卷积可用其循环卷积代替而不发生混叠,必须选择循环卷积长度N≥N1+N2-1,即将x(n)和h(n)补零至长度为N的序列,即:

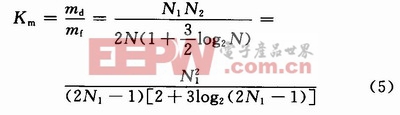

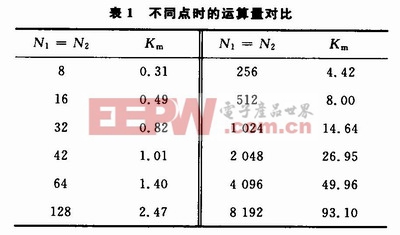

在基于FFT的FIR滤波器结构中,求X(k),H(k)以及反傅里叶变换y(n)需要的乘法次数均为N/2log2N,而计算X(k)H(k)需要N次乘法,所以基于FFT的总乘法次数为mf=3/2Nlog2N+N。由于h(n)满足式(3)条件,所以直接卷积所需的乘法次数为md=1/2N1N2。假设N1=N2,则比较这两种乘法计算量有:

从表1可知,当N142时,FFT法的运算量小于直接卷积的运算量,当N1=42时,FFT法的运算量与直接卷积的运算量相当,当N1>42时,FFT法的运算量大于直接卷积的运算量,并且随着N1增加,FFT法的运算速度越来越快,特别是N1=8 192时,FFT法的运算速度与直接卷积相比快上将近100倍。

2.5 分布式结构

2.5.1 分布式算法原理

分布式算法(distributed arithmetic,DA)于1973年就由Croisier提出,但是直到FPGA出现,才广泛的被应用于FPGA中计算乘累积和。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码