FIR滤波器的FPGA实现方法

对于有符号数x(n)可以用下式的补码形式表示:

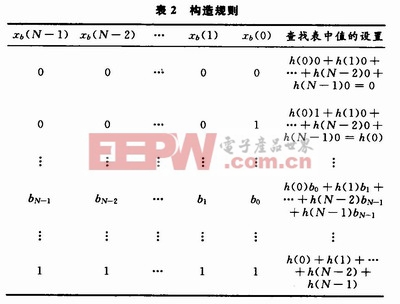

对于式(7)中的h(i)xb(n-i)代表着输入数据x(n-i)的第i位与抽头系数h(i)的乘积,对于FIR滤波器,其系数h(i)是常数,所以可以事先构造一个查找表。该查找表存储所有h(i)xb(n-i)的乘积值,通过输入(xb(N-1),xb(N-2),…,xb(0))对该表寻址,然后将查得的值乘上2b后移位累加便得到滤波器输出y(n)。该查找表构造规则如表2所示。

2.5.2 基于分布式算法的FIR滤波器结构

基于分布式算法的FIR滤波器主要有3种结构类型。

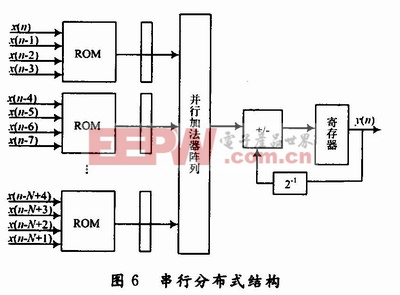

(1)第一种结构为串行分布式结构。串行分布式FIR滤波器的原理为,首先用所有N个输入量的最低位对DA查找表进行寻址查值,得到一个部分积,将部分积右移一位即相当于除以2后放到寄存器中暂存。同时,N个输入量的次低位开始对DA查找表进行寻址查值,得到另一个部分积,把该部分积与上一个储存在寄存器中的值进行相加,相加后的值再右移一位放到寄存器中。以此重复循环累加,直到所有位数都寻址完

成,注意最高位寻址后的部分积是相减,最后所得到的值就是所需要的结果。

当N过大,即FIR滤波器的滤波阶数很高时,采用一个查找表来实现将使得存储查找表的ROM变得十分庞大。为此可采用部分表结构,即将查找表划分为多个部分,N个输入量的同一位对应不同的部分表寻址。图6所示即为基于4输入部分表结构的串行DA结构。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码