14位125MSPS四通道ADC电路图(通过后端数字求和增强SNR性能)

电路功能与优势

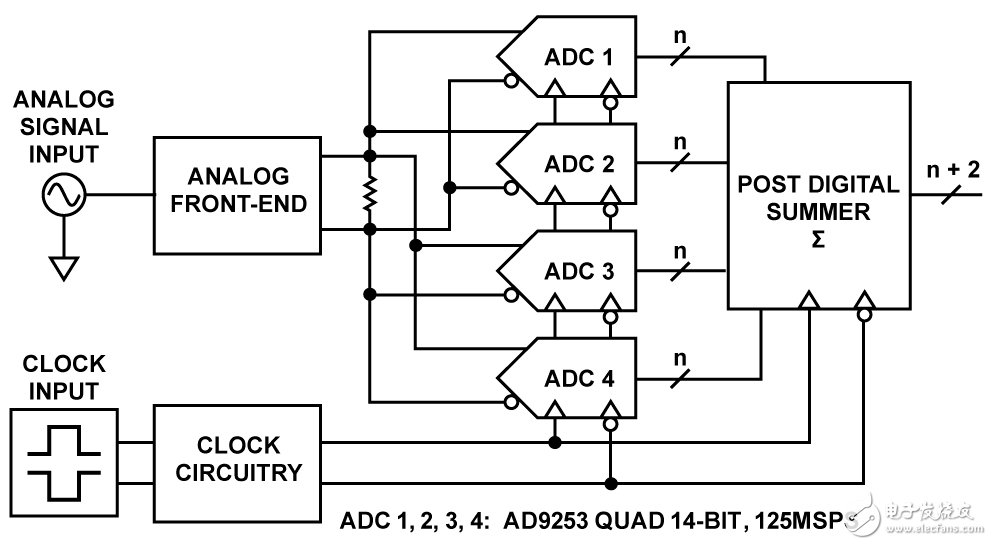

图1所示电路是14位、125 MSPS四通道ADC系统的简化图,该电路使用后端数字求和将信噪比(SNR)从单通道ADC的 74 dBFS提升到四通道ADC的78.5 dBFS。这项技术特别适合要求高SNR(如超声和雷达)的应用,并且利用了现代高性能、低功耗、四通道流水线式ADC。

该电路使用了非相关噪声源在方和根(rss)基础上相加,而信号电压在线性基础上相加的基本原理。

图1. 四个并联ADC求和得到更高SNR的基本框图

电路描述

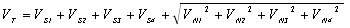

每个ADC的输入由信号项(VS)和噪声项(VN)组成。将四个噪声电压源求和可得到总电压 VT, 它是四个信号电压加上四个噪声电压方和根的线性和,例如:

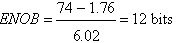

由于VS1 = VS2 = VS3 = VS4,信号可有效地乘以4,而转换器噪声——具有等效rms值——仅乘以2,因此信噪比以系数2增加,即6.02 dB。所以,6.02 dB的SNR增量是将四个类似信号求和所引起的一个额外的有效分辨率位的结果。由于 SNR(dB) = 6.02N + 1.76 dB,其中N为位数,从而

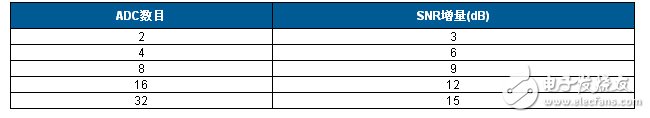

表1显示将多个ADC输出求和得到的SNR理论值。为方便起见,显然应选择将四个ADC求和。某些关键情况下可能需要更多的ADC求和,但具体取决于其他的系统规格(包括成本)和可用的电路板空间。

表1. 增加SNR与ADC数目的关系ADC数目SNR增量(dB)

14位ADC的理想SNR是(6.02 × 14) + 1.76 = 86.04 dB AD9253 数据手册指定的典型SNR为74 dB,但其产生的ENOB为12位。

图1所示电路集成无源接收器前端,由四个模拟输入通道组成,采用器件为14位、125 MSPS四通道模数转换器 AD9253 。

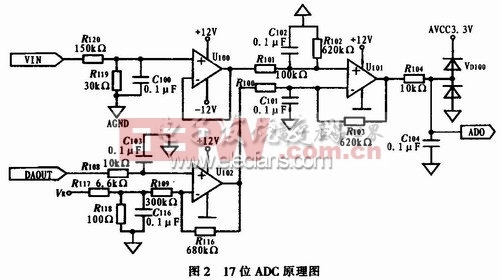

该电路接受单端输入,并通过双平衡配置中两个阻抗比为 1:1的宽带宽(3GHz) M/A-COM ETC1-1-13巴伦将输入转换为差分信号,如图2所示。

图2. 输入模拟求和网络

所有四个ADC输入均在巴伦配置的次级侧相连。电路中无增益,每个模拟输入对都有简单滤波功能,减少可能反馈至邻近ADC通道的残余反冲信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码