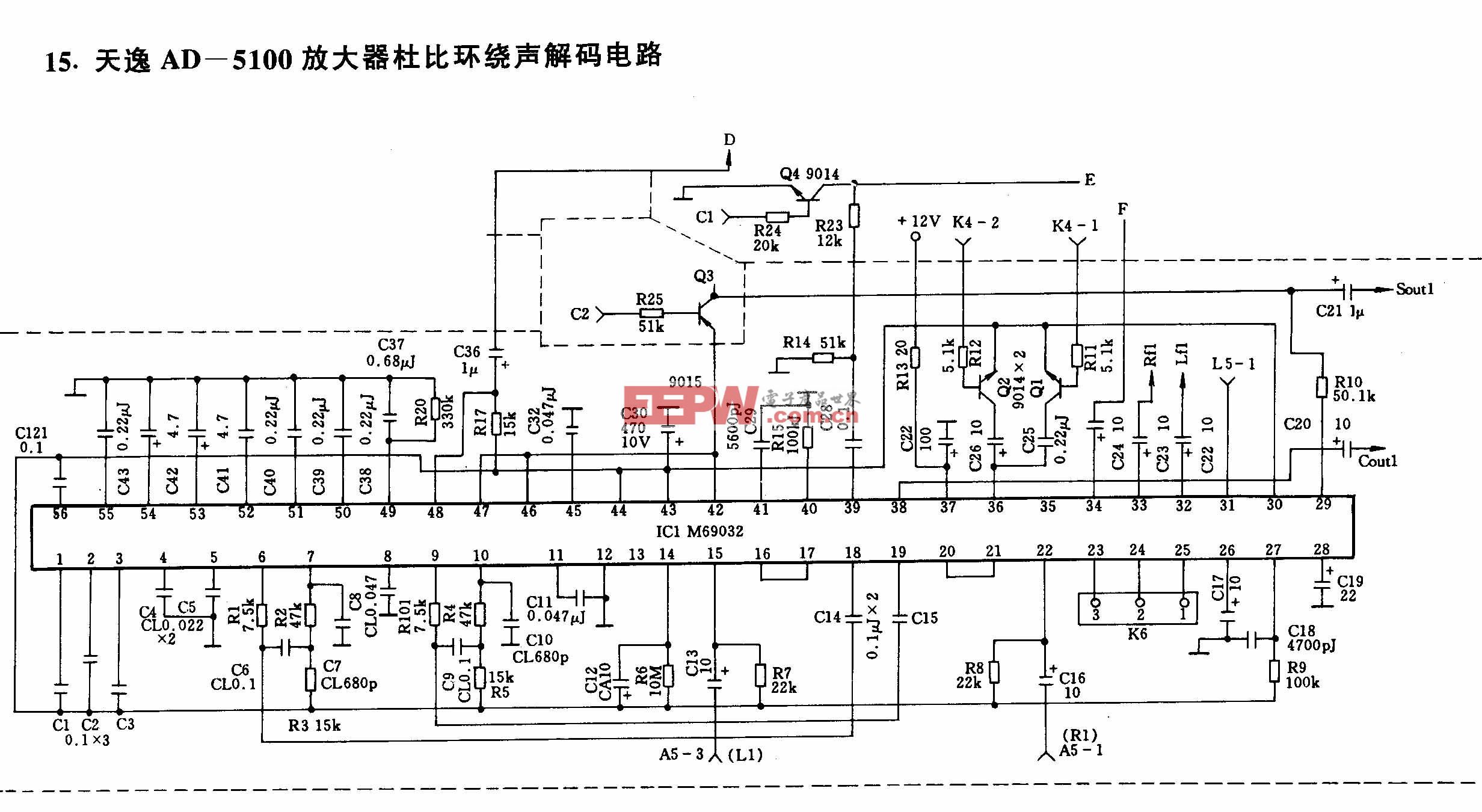

利用开关稳压器PMU ADP5020为八通道超声ADC/LNA/VGA/AAF AD9272供电,以提高效率 (CN0135)

本电路利用电源管理单元ADP5020 提供八通道LNA/VGA/AAF/ADC和交叉点开关AD9272所需的各供电轨。

ADP5020是一款低噪声电源管理单元(PMU),可提供三路输出:两个同步降压通道(分别为600 mA和250 mA)和一个低压差线性稳压器(LDO)通道(150 mA)。该电路的输入电压采用+5.5 V。

AD9272针对超声应用进行了优化,具有一条时间增益压缩路径,它采用八通道低噪声放大器(LNA)、衰减范围为42 dB的可变增益放大器(VGA)、8 MHz至18 MHz抗混叠滤波器以及12位10 MSPS至80 MSPS ADC。CW多普勒路径含有一个八通道、完全差分交叉点开关,用于电流输出求和。对于低功耗至关重要的便携式超声应用,若需使用多个AD927x器件,这就是一种理想的解决方案。

图1显示该ADP5020电源解决方案,它为八通道LNA/VGA/AAF/ADC和交叉点开关AD9272提供所需的全部输入供电轨。ADP5020的输入为+5.5 V低纹波直流总线电源。ADP5020输出经过配置,与AD9272所需的各电源相连,包括AVDD2 (+3.0 V/363 mA)电源、AVDD1 (+1.8 V/209 mA)电源和DRVDD (+1.8 V/50 mA)电源。ADP5020的开关频率为3 MHz,允许使用较小、成本较低的电感。与利用三个独立的低压差(LDO)稳压器及其支持器件的方案相比,本电路所用器件的数量更少。

图1. ADP5020与AD9272相连(原理示意图,未显示去耦和所有连接)

每个电源输出端均用一个简单的滤波器,它由一个表贴芯片铁氧体磁珠(FB)和并联的10 μF电容与0.1 μF电容组成。滤波器之后,这些电压分配至PCB的电源层,其中各IC均额外进行局部去耦。采用5 MHz模拟输入频率和40 MSPS采样时钟时,所产生的测试结果如图2所示。图中所示为最大增益设置(零衰减或+1.6 V)情况下GAIN+引脚上的FFT输出频谱。

图2. 5 MHz AIN、最高增益(0 dB衰减)、采样速率 = 40 MSPS、采用ADP5020电源的输出频谱

图2. 5 MHz AIN、最高增益(0 dB衰减)、采样速率 = 40 MSPS、采用ADP5020电源的输出频谱

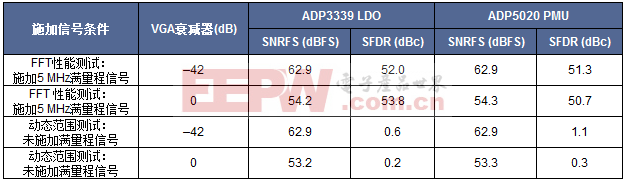

表1显示采用线性稳压器(ADP3339系列的1.8 V和3.0 V版本)和ADP5020两种情况下,AD9272上测得的数据。主要是针对两种VGA增益设置(0 dB和−42 dB)的满量程信噪比(SNRFS)和无杂散动态范围(SFDR)。

表1所示的另一项测试为动态范围测试。这种测试中,不施加任何信号,而是将输入端接,以便利用FFT测量本底噪声。

表1. 采用ADP3339系列LDO与采用ADP5020 PMU时的AD9272性能对比1

1 其它测试条件:LNA增益 = 21 dB,PGA增益 = 30 dB,采样频率 = 40 MSPS。

总之,采用ADP5020开关稳压器设计时,SNR、SFDR或动态范围性能没有任何下降。FFT本底噪声响应几乎完全一致,并且没有任何与开关频率相关的可测量频率成分。

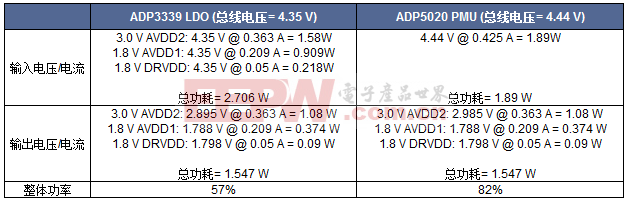

表2中的功效比计算将LDO稳压器设计与开关稳压器设计的整体功效比进行了比较。为了合理比较利用各稳压器方案的输入至输出计算得到的功率损失,本实验所用的两种评估板均采用相同的线内或总线电压。开关稳压器(ADP5020)设计的整体功率提高了25%。对于单个AD9272,这大约节省800 mW功耗。如果系统中使用多个器件,节省的功耗将相当可观。

适当的布局和电路分割是确保设计成功的关键。PCB堆叠(电源层和接地层)应紧密耦合,以改善旁路。开关稳压器电感应安装在PCB背面,以利于消除耦合至敏感器件的磁通量。充分的电源滤波至关重要。应使用两级输出滤波器,以降低纹波并衰减噪声。还应仔细了解电流流向,以及器件或相邻电路布局。电路之间应有良好的隔离。

ADC负载电流基本上保持稳定,并与采样时钟频率成比例。因此,开关稳压器的瞬态响应不像在阶梯式负载应用设计中那样重要,例如驱动FPGA等。

该电路开关稳压器部分的布局尤其重要;应以ADP5020 评估板 为指南。

欲了解设计和测试结果的更多信息,请参考Rob Reeder和Michael Cobb主持的网络研讨会 高速模数转换器应用中的开关稳压器设计 ,以及Michael Cobb撰写的技术文章“利用开关电源为高速模数转换器供电”。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码