集成ECC的CMOS静态RAM ,支持单双芯片使能

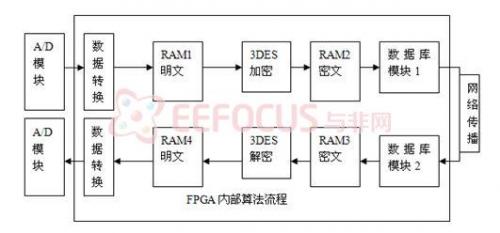

CY7C1041G和CY7C1041GE是由Cypress推出的带嵌入式ECC(纠错码)的高性能CMOS快速静态RAM器件。这两种器件均支持单、双芯片使能选项,以及多种引脚配置。CY7C1041GE器件具有一个ERR引脚,用于通知读周期中的错误检测和纠正事件。通过将芯片使能(CE)、写入使能输入(WE)设置为低电平,并分别在器件数据引脚(I/O0 至I/O15)、地址引脚(A0 到A17)提供数据及地址,即可执行数据写入操作。

产品通过控制字节高电平使能(BHE)和字节低电平使能(BLE)的输入,来进行高字节、低字节写入指定存储器位置的操作。BHE 控制I/O8 至I/O15脚;BLE控制I/O0 至I/O7脚。通过设置芯片使能(CE)及输出使能(OE)输入为低电平,并提供地址上行所需的地址,便能执行读取操作,在I/O 线上(I/O0 至I/O15)读取数据。通过设置所需的字节使能信号(BHE或BLE),可以执行字节访问,即读取指定地址上高字节或低字节数据。

CY7C1041G/CY7C1041GE的特性:

-高速:tAA = 10 ns

-用于单比特错误纠正的嵌入式纠错码(ECC)

-活动模式和待机模式只需低电流

有效电流ICC = 38 mA (典型值)

待机电流ISB2 = 6 mA (典型值)

-工作电压范围:1.65 V至2.2 V,2.2 V至3.6 V,4.5 V至5.5 V

-1.0 V 数据保持

-TTL — 各兼容输入与输出

-错误指示(ERR)引脚用于表示单位错误的检测及纠正

-无铅44引脚SOJ、44引脚TSOP II和48球形焊盘VFBGA封装

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码