去耦电容,是“耦”了什么?非要“去”了?

“去耦” 中的 “耦” 原指耦合,在电路里,耦合表示两个或多个电路部分之间存在相互影响、相互干扰的电气连接关系。去耦电容名字里的 “去耦”,意在减少电路不同部分之间不必要的耦合干扰,具体原理如下:

切断高频干扰传导路径:在电子电路系统中,不同的电路模块、器件各自工作,由于共用电源线路,一个模块产生的高频噪声很容易顺着电源线 “串门”,干扰到其他正常工作的模块,这就是一种耦合现象。去耦电容利用自身特性,为高频信号提供一条低阻抗的旁路通道,让高频噪声优先通过电容流入地,而非沿着电源线乱窜,切断了高频干扰在电路各部分之间的传导路径。

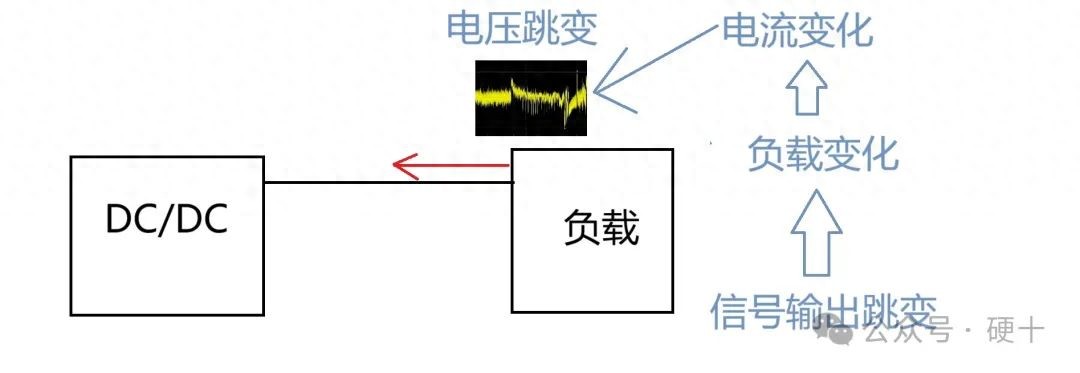

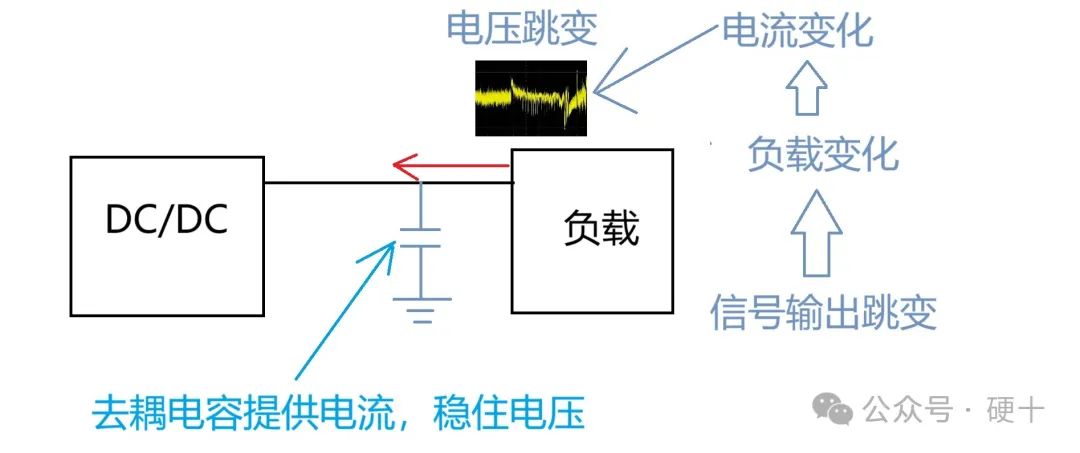

减弱数字电路与供电电源间的耦合:数字电路在运行时,瞬间电流需求变化剧烈,电源与电路之间因为电流传输就产生了紧密的耦合。一旦电源受干扰波动,电路工作状态也受影响;反过来,电路产生的电流冲击也干扰电源稳定性。去耦电容并联在电源和地之间,靠近需要稳定供电的芯片等器件,当电路电流需求突变时,电容及时补充或吸纳电能,缓冲电流冲击,弱化电源与电路之间因为电流传输造成的强耦合,让电路和电源相对独立稳定工作。

一般硬件工程师都知道,去耦电容是为了使得电源线上的电压更平滑,为电路中的各个元件提供更 “干净” 的供电环境,防止因电源噪声引发电路误动作。但是很多人,只知道把电源搞干净,但是是把哪部分的噪声搞干净都没搞清楚。

“负载瞬态电流”,这个问题不是由电源输出端的电源模块或者电源芯片所产生,而是由用电负载自身的负载变化所产生,这个负载变化又是由于大量数字信号在“跳变”所产生。电子电路工作时,各器件会在不同时刻从电源汲取电流,这种电流的快速变化会在电源线上产生高频的电压波动,也就是噪声。去耦电容具有储能特性,当器件瞬间需要大电流时,它能快速释放储存的电能来补充,避免电源电压瞬间被拉低;而在器件汲取电流较小时,电容又会充电储存多余电能。

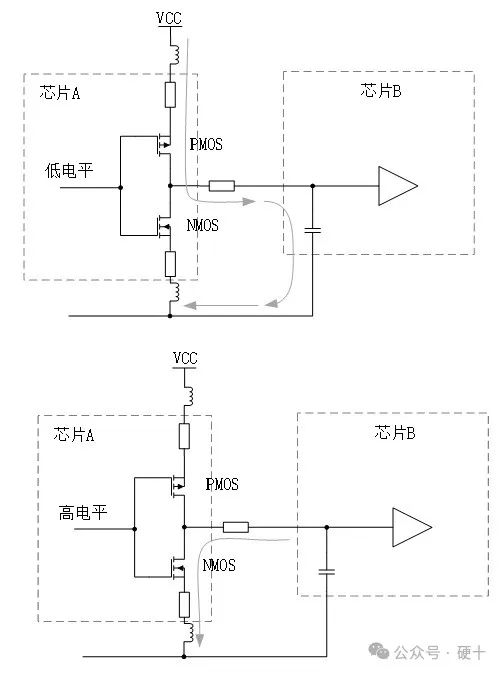

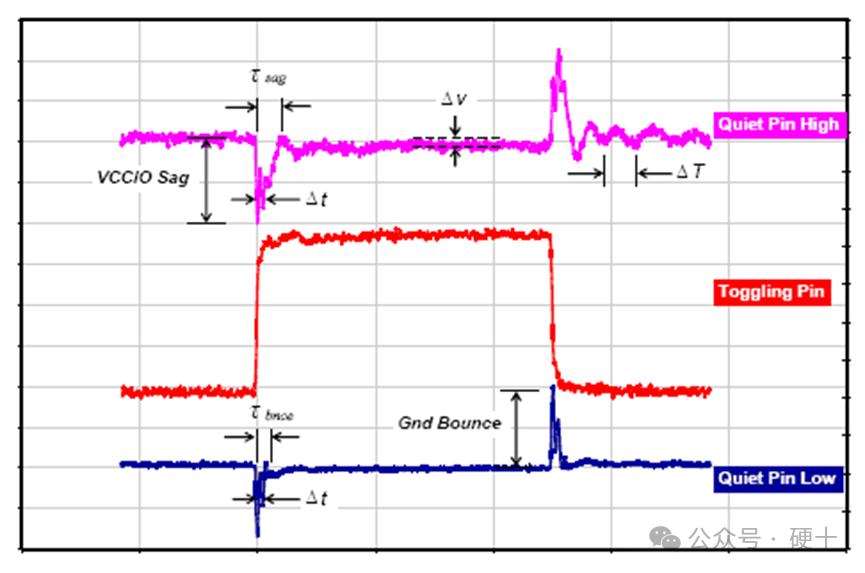

当控制信号是一个低电平的时候,上面PMOS打开,此时输出是高电平。打开的瞬间,VCC通过LVCC和R,对芯片B的输入管脚进行充电。当控制信号是一个高电平的时候,下面的NMOS打开,此时输出的是低电平。打开的瞬间,芯片B的输入管脚储存的电量经过NMOS进行放电。在CMOS反相器输出状态发生变化的时候,流过的电流正是变化的电流。于是,在走线、过孔、平面层和封装(键合引线、引脚)等这些具有电感的连接部件上,便会感应出电压。例如标准的GND地电位应该是0V,但是芯片与地之间的链接部件存在电感,就会感应出电压VGND,那么芯片上的“地”电位就被抬高了,高于0V。

当CMOS输出信号同时从低电平到高电平切换时,VCC上会观测到一个负电压的噪声,同时也会影响到GND,并有可能引起一个振荡。当输出信号从高电平到低电平切换时, GND上会观测到一个正电压的噪声,同时也会影响到VCC,并有可能引起一个振荡。

我们的最终设计目标是,不论负载瞬态电流如何变化,都要保持负载两端电压变化范围很小,这个要求等效于电源系统的阻抗Z要足够低。我们是通过去耦电容来达到这一要求的,因此从等效的角度出发,可以说去耦电容降低了电源系统的阻抗。另一方面,从电路原理的角度来说,可得到同样结论。电容对于交流信号呈现低阻抗特性,因此加入电容,实际上也确实降低了电源系统的交流阻抗。

从阻抗的角度理解电容退耦,可以给我们设计电源分配系统带来极大的方便。实际上,电源分配系统设计的最根本的原则就是使阻抗最小。最有效的设计方法就是在这个原则指导下产生的。

所以,电源系统的去耦设计的一个原则,就是在感兴趣的频率范围内,使整个电源分配系统的阻抗最低。其方法是用去耦电容,那么用多大的电容能满足要求?如何确定这个值?选择哪些电容值?放多少电容?如何安放在电路板上?电容放置距离有什么要求?

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码