RISC与CISC

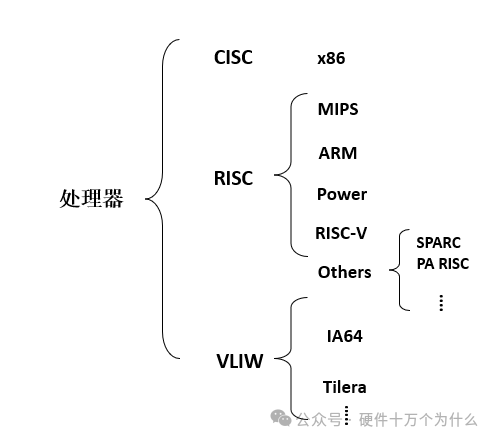

CISC(复杂指令集计算)和RISC(精简指令集计算)是两种不同的计算机指令集架构。

CISC(Complex Instruction Set Computing)

复杂指令集:CISC架构设计了大量的复杂指令,每条指令可以完成较为复杂的操作。

较少的指令数:因为每条指令可以完成较多的操作,所以总体的指令数较少。

内存使用效率高:由于指令的复杂性,单个指令可以在较少的时钟周期内完成任务,从而减少内存带宽的占用。

硬件实现复杂:实现这些复杂指令需要更复杂的硬件逻辑。

常见应用:早期的计算机和一些特定应用中使用较多,如x86架构。

RISC(Reduced Instruction Set Computing)

精简指令集:RISC架构设计了一组相对简单且数量较少的指令,每条指令执行一个非常简单的操作。

较多的指令数:由于每条指令执行的操作简单,完成一个任务需要更多的指令。

指令执行速度快:简单指令可以在一个时钟周期内完成,从而提高了指令执行速度。

硬件实现简单:由于指令集的精简,硬件设计相对简单且更容易优化。

常见应用:现代嵌入式系统和移动设备中广泛使用,如ARM架构。

对比

复杂性:CISC指令复杂,RISC指令简单。

执行速度:RISC通常具有更快的执行速度,因为每条指令在一个时钟周期内完成。

指令数:CISC指令数少,但每条指令功能强大;RISC指令数多,但每条指令功能简单。

硬件设计:CISC硬件设计复杂,RISC硬件设计简单。

应用领域:CISC多用于台式机和服务器,RISC多用于嵌入式系统和移动设备。

这两种架构各有优劣,具体选择取决于应用场景和性能需求。

RISC和CISC的对比

RISC(Reduced Instruction Set Computer)

定义:RISC是一种执行较少类型计算机指令的微处理器架构。通过减少指令集的数量,可以更快地执行操作。

起源:1974年,纽约约克镇IBM研究中心的John Cocke提出了RISC的概念。他发现计算机中约20%的指令承担了80%的工作。

主要特点:

指令简单:RISC设计者将主要精力放在经常使用的简单指令上,这些指令可以在一个时钟周期内完成。

指令数少:较少的指令类型需要更少的晶体管和电路元件,从而简化微处理器设计,提高执行速度。

存储器操作限制:对存储器操作有限制,使控制简单化。

程序复杂性:由于简单的指令集,实现复杂功能时需要组合多条指令,程序复杂度增加,内存占用较大。

中断处理:可以在一条指令执行的适当位置响应中断。

CPU芯片电路:包含较少的单元电路,面积小、功耗低。

设计周期短:结构简单,布局紧凑,设计周期短,易于采用最新技术。

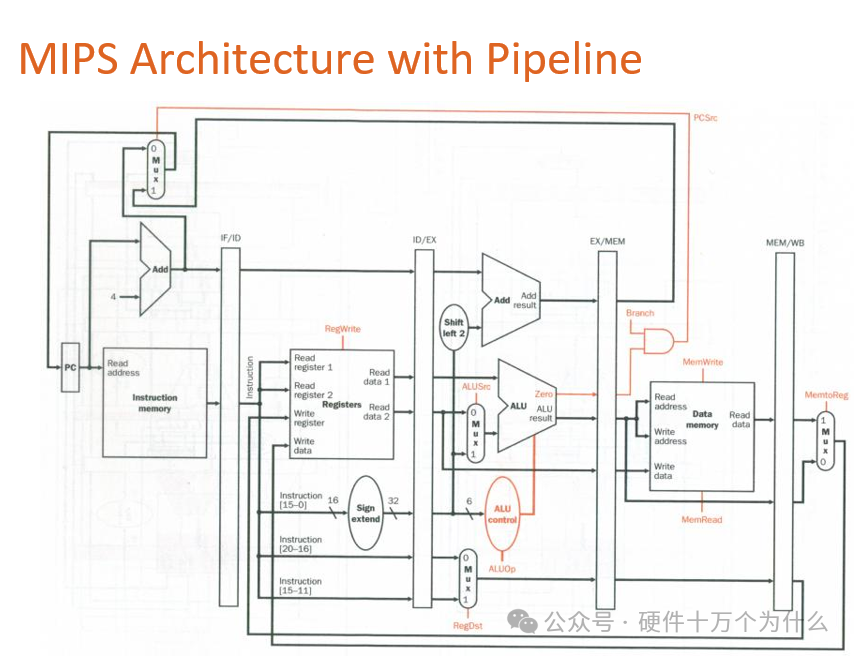

常见处理器:DEC Alpha、ARC、ARM、MIPS、PowerPC、SPARC、SuperH等。

CISC(Complex Instruction Set Computer)

定义:CISC是一种复杂指令集计算机架构,使用丰富的指令集,每条指令可以完成较为复杂的操作。

主要特点:

指令丰富:指令系统比较丰富,有专用指令来完成特定功能。

存储器操作直接:存储器操作指令多,操作直接。

程序简单性:汇编语言程序编写相对简单,特别是科学计算及复杂操作的程序设计效率较高。

中断处理:在一条指令执行结束后响应中断。

CPU芯片电路:包含丰富的电路单元,功能强大,但面积大、功耗高。

设计周期长:结构复杂,设计周期长。

用户使用:功能强大,实现特殊功能容易。

常见处理器:X86。

RISC和CISC的区别

指令系统:

RISC:专注于简单、高效的常用指令,通过组合指令完成不常用功能。

CISC:提供丰富的指令系统,有专用指令完成特定功能。

存储器操作:

RISC:对存储器操作有限制,控制简单。

CISC:存储器操作指令多,操作直接。

程序复杂性:

RISC:程序复杂,需要较大内存空间。

CISC:程序编写相对简单,设计效率高。

中断处理:

RISC:在一条指令执行的适当位置响应中断。

CISC:在一条指令执行结束后响应中断。

CPU芯片电路:

RISC:单元电路少,面积小、功耗低。

CISC:电路单元丰富,面积大、功耗高。

设计周期:

RISC:设计周期短,易于采用新技术。

CISC:设计周期长,结构复杂。

用户使用:

RISC:指令规整,性能容易把握,易学易用。

CISC:结构复杂,功能强大,实现特殊功能容易。

应用范围:

RISC:更适合于专用机。

CISC:更适合于通用机。

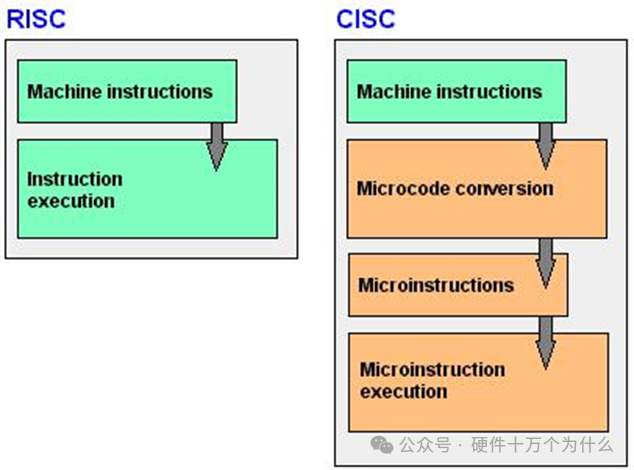

指令解码和执行效率:RISC核心设计简单,指令集较少,容易进行指令解码和执行优化。因此,在现代CISC处理器中,首先将复杂的CISC指令解码成更简单的RISC微操作(micro-operations),再由RISC核心执行。这种方式可以提高指令执行效率。

设计复杂性降低:RISC核心的设计相对简单,可以简化处理器设计的复杂性。通过在CISC处理器中采用RISC核心,可以降低设计和验证的难度,缩短开发周期。

能效比提升:RISC核心因为其简单的设计,通常具有较低的功耗和较小的芯片面积。这对于移动设备和嵌入式系统等功耗敏感的应用场景尤为重要。

模块化设计:通过使用RISC核心,处理器设计可以更加模块化和灵活。这使得在同一架构下可以更容易地进行不同型号和规格处理器的扩展和开发。

兼顾旧有软件支持和新性能:现代CISC处理器(如x86架构)需要兼容大量已有的软件和系统,因此外部接口依然保持CISC架构。但是,内部通过RISC核心执行,可以兼顾性能和兼容性,提供更好的用户体验。

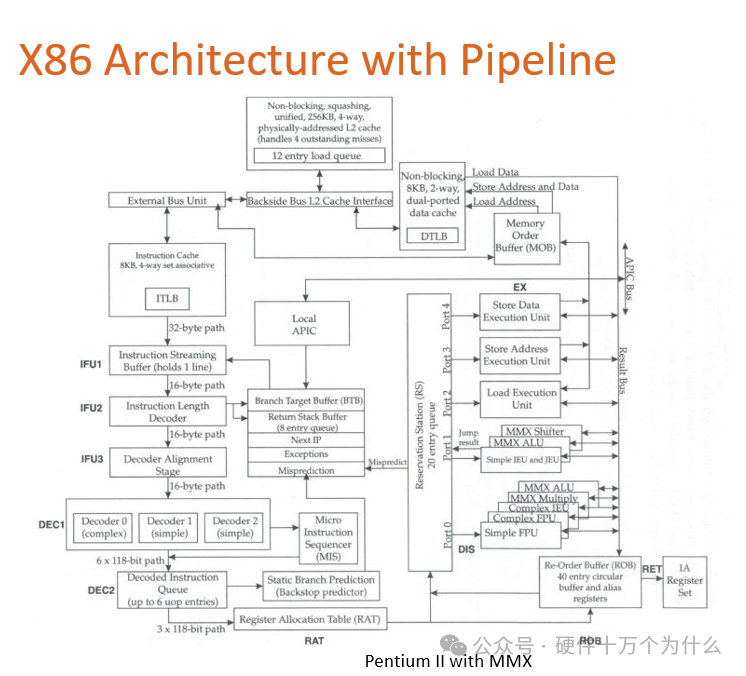

微操作:Intel的x86处理器内部使用了一种被称为“微操作(micro-ops)”的机制,将复杂的x86指令解码为更简单的微操作,然后由内部的RISC风格的执行单元处理。

超标量和超流水:现代x86处理器利用超标量和超流水技术,同时执行多条微操作,以提高指令级并行度和处理速度。

这两种架构各有优劣,具体选择取决于应用场景和性能需求。

为什么现在CISC也是由RISC实现?

如今的CISC处理器都参考了RISC设计,将指令在处理器内翻译成微码再工作。

1. 性能优化

2. 设计简化和时间缩短

3. 功耗和面积优化

4. 灵活性和可扩展性

5. 兼容性和性能平衡

Intel x86架构

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码