CMOS反相器的功耗

本文解释了CMOS反相器电路中的动态和静态功耗。

为集成电路提供基本功能的CMOS反相器的发展是技术史上的一个转折点。这种逻辑电路突出了使CMOS特别适合高密度、高性能数字系统的电气特性。

CMOS的一个优点是它的效率。CMOS逻辑只有在改变状态时才需要电流——简单地保持逻辑高或逻辑低电压的CMOS电路消耗的功率非常小。一般来说,低功耗是一个理想的功能,当你试图将尽可能多的晶体管功能封装在一个小空间中时,这尤其有益。

正如计算机CPU爱好者提醒我们的那样,充分去除集成电路中的热量可能很困难。如果没有CMOS反相器和其他类似的CMOS电路,这将更加困难。在这篇由三部分组成的系列文章中,我们将回顾CMOS反相器的关键特性,并讨论其两种主要的功耗类型:动态和静态。在接下来的两篇文章中,我们将更深入地研究动态功耗。

CMOS反相器的结构和操作

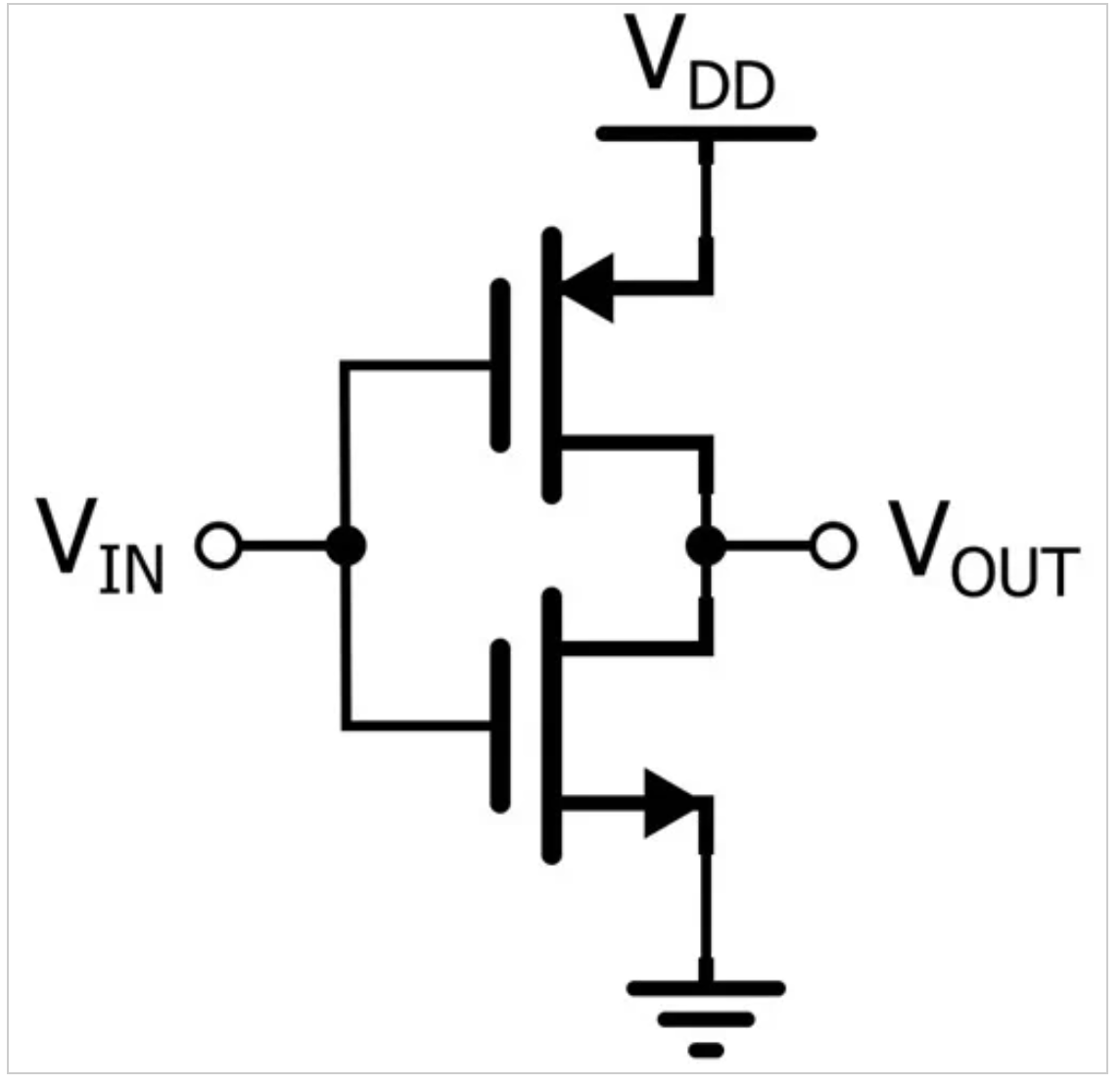

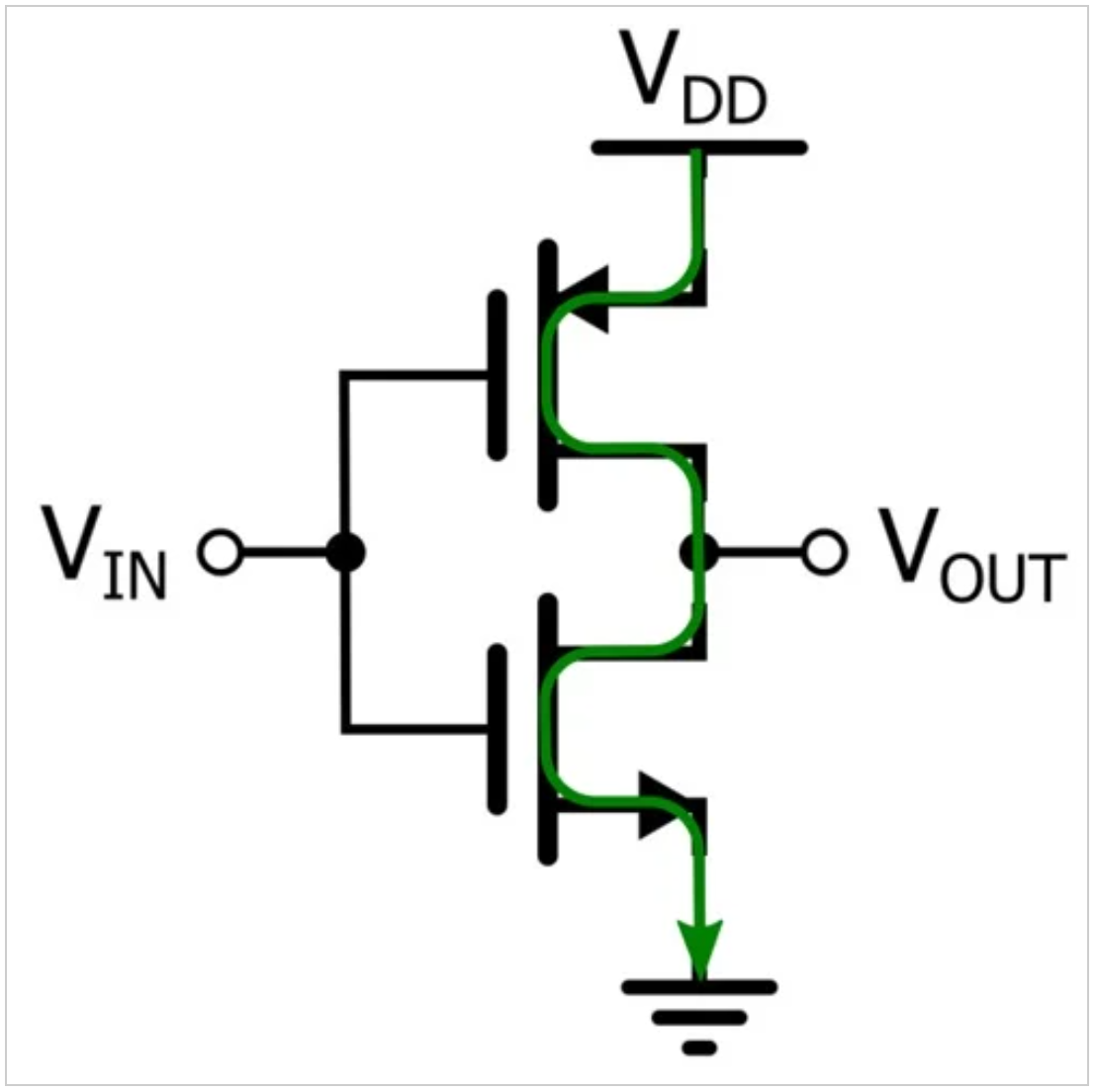

CMOS反相器由连接在一起的NMOS晶体管和PMOS晶体管组成。图1显示了基本CMOS反相器的示意图。

基本CMOS反相器电路的示意图。

图1。CMOS数字反相器使用一个NMOS和一个PMOS晶体管。

CMOS反相器的基本操作非常简单:

当输入端被驱动到逻辑高电压时,上PMOS晶体管阻断电流,下NMOS晶体管传导电流。因此,输出端子通过低电阻路径连接到0V。

当输入端子被驱动到逻辑低电压时,PMOS导通并且NMOS截止。输出通过低电阻路径连接到VDD。

以这种方式,逻辑高输入产生逻辑低输出,而逻辑低输入产生逻辑高输出。

动态功耗

每当电流流过导电元件时,就会消耗电力。我们在电力的基本公式中看到了这种关系:

等式1。

尽管CMOS反相器在稳定状态下不需要电流,但在其逻辑转换过程中会消耗功率。这种动态功率损耗有两种类型:

开关功耗。

短路功耗。

让我们来看看每一个。

开关功耗

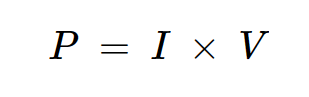

当输入逻辑转换发生时,为了对电路中的电容进行充电或放电,必须流过瞬态电流。在从低到高的输出转换期间,当输出电压增加到VDD时,电流流动以对负载电容充电。图2显示了这股电流所经过的路径。

在从低到高的输出转换过程中,通过CMOS反相器的充电电流的流动。

图2:在低到高输出转换期间充电电流的流动。

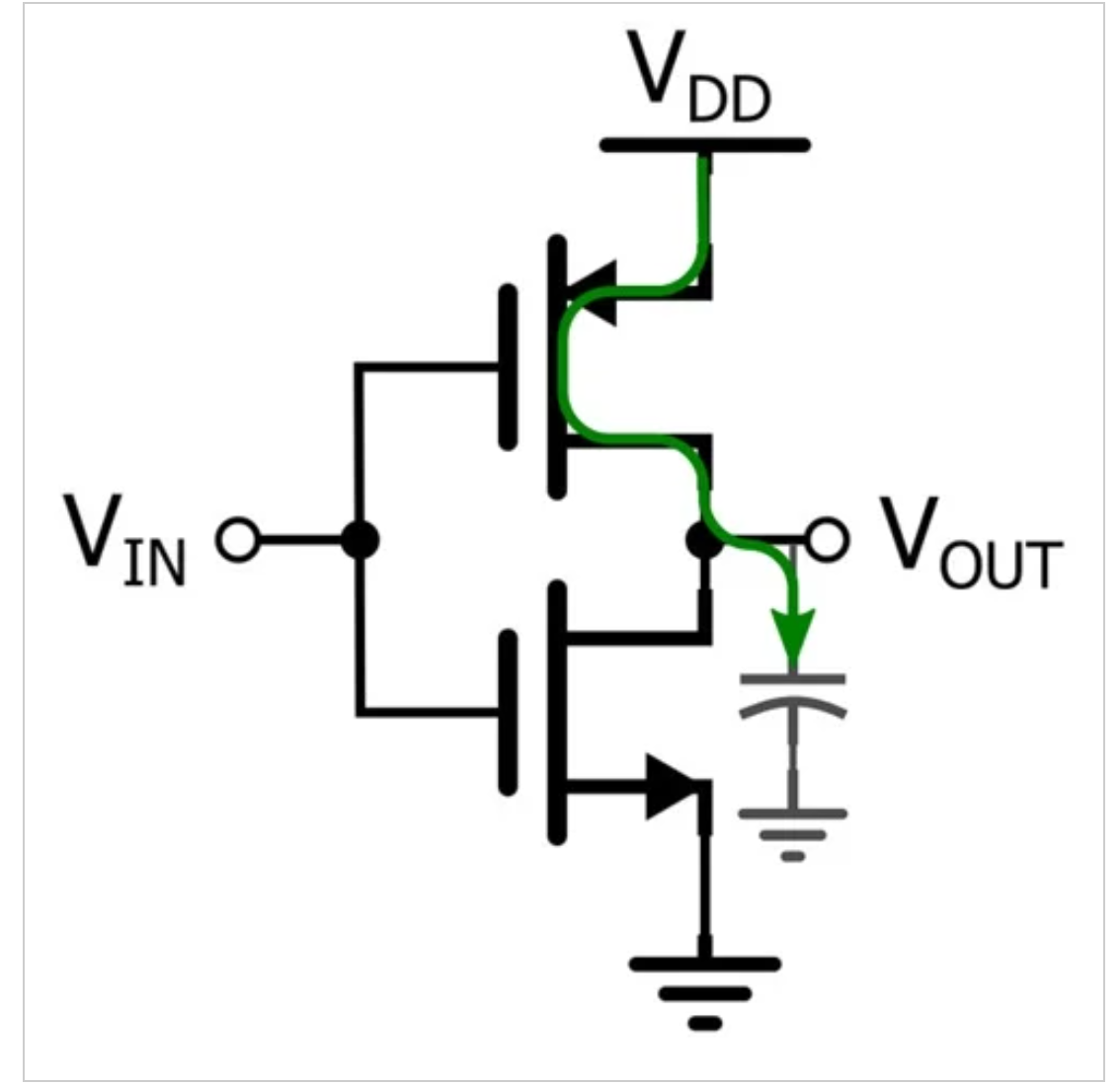

电流也在从高到低的输出转换过程中流动(图3),随着输出电压降低到地电位,电容放电。

在高到低输出转换期间,通过CMOS反相器的放电电流的流动。

图3。在高输出到低输出转换期间的放电电流的流动。

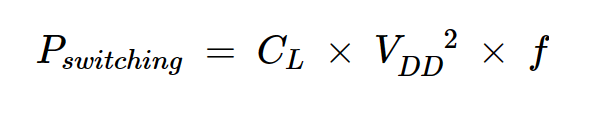

为了估计CMOS反相器的开关损耗,我们使用以下方程:

等式2。

都是什么

CL是预期的负载电容

f是开关频率。

CL×VDD2计算一个开关周期所需的能量。为了将这个结果从能量转换为功率,我们将其乘以每秒循环次数(f),得到上面的方程。

短路功率耗散

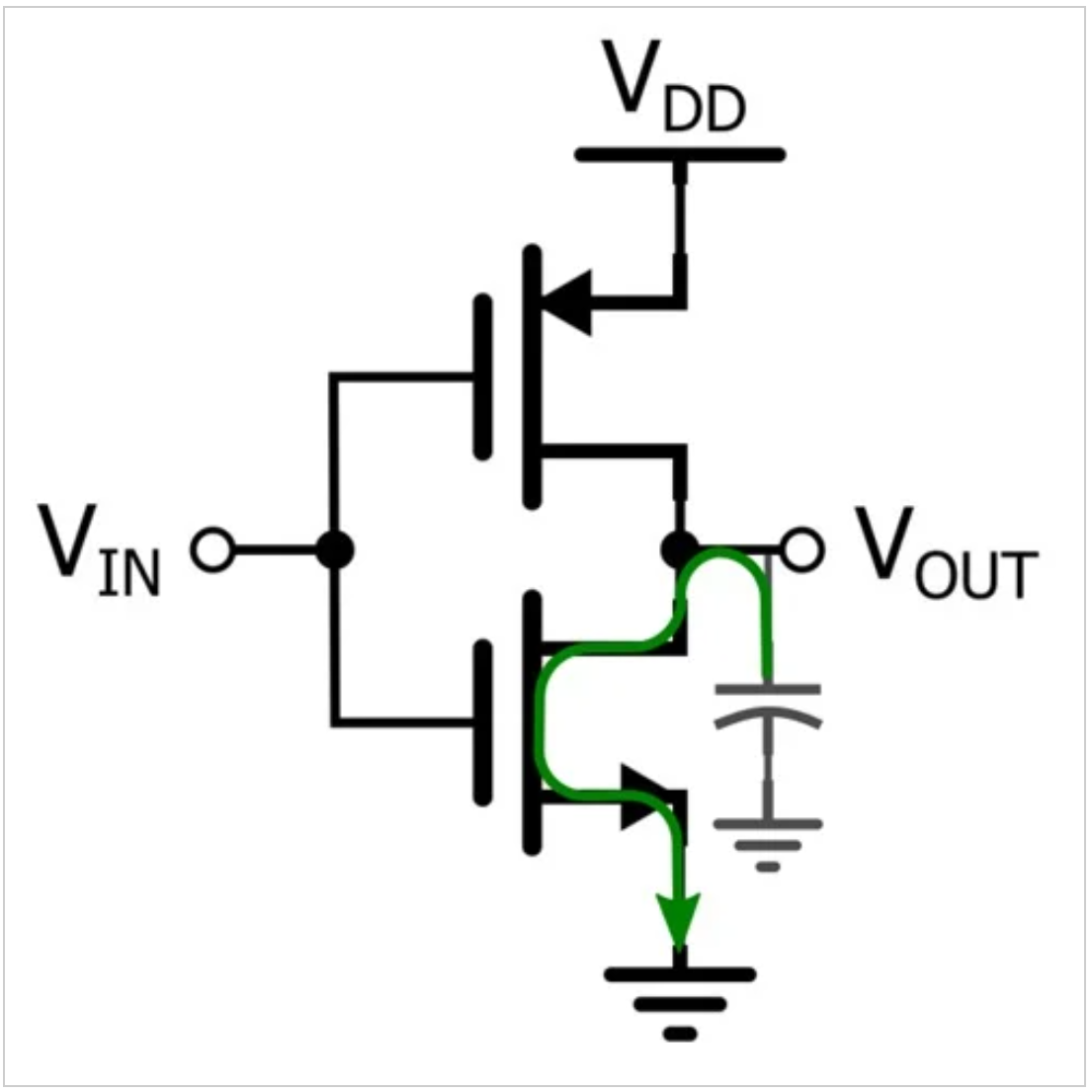

另一种类型的动态功耗是由短路电流引起的。也称为击穿电流,这是逆变器逻辑电平转换期间发生的瞬态情况。

当CMOS反相器稳定在逻辑状态时,其两个晶体管中的一个处于非导通模式。因此,电流不容易从VDD流到地。然而,当反相器改变状态时,会有一个短暂的交叉期,在此期间NMOS和PMOS都具有一定程度的导电性。当电流流过产生的短路时,能量会损失(图4)。

短路电流发生在逆变器的逻辑电平转换期间。

图4。NMOS和PMOS晶体管在逻辑电平转换期间短暂地产生短路,允许电流从VDD流到地。

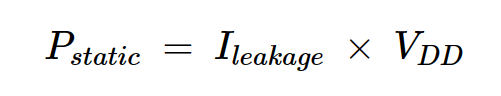

静态功耗

在这篇文章中,我避免说“CMOS反相器中绝对不会发生稳态功耗”之类的话。事实上,场效应晶体管并不是理想的开关。即使在关断状态下,漏电流也可以从漏极流到源极,以及从漏极或源极流到衬底。

如果这些泄漏电流的大小是已知的,则可以使用以下公式计算得到的功率耗散:

等式3。

动态功耗过去远高于静态功耗。如今,静态功率可能非常重要。随着CMOS特征尺寸的减小,其对总功耗的贡献接近动态功率。

最后,请注意,静态功率是工作温度的函数。随着温度的升高,静态功耗也会增加。

总结

CMOS反相器既可用作独立的逻辑运算,也可用作高阶逻辑运算的组件。CMOS反相器也用于在具有低驱动能力的数字电路的输出处创建缓冲器。反相器提供模拟放大以减少信号的上升和下降时间。它们还可以将信号恢复到完全逻辑电平。

在这篇文章中,我们简要地讨论了CMOS反相器的操作,并检查了这个基本逻辑电路的动态和静态功耗。在本系列的下两篇文章中,我们将使用LTspice模拟来更详细地探讨动态功耗的主题。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码