新思科技面向台积公司先进工艺加速下一代芯片创新

摘要:

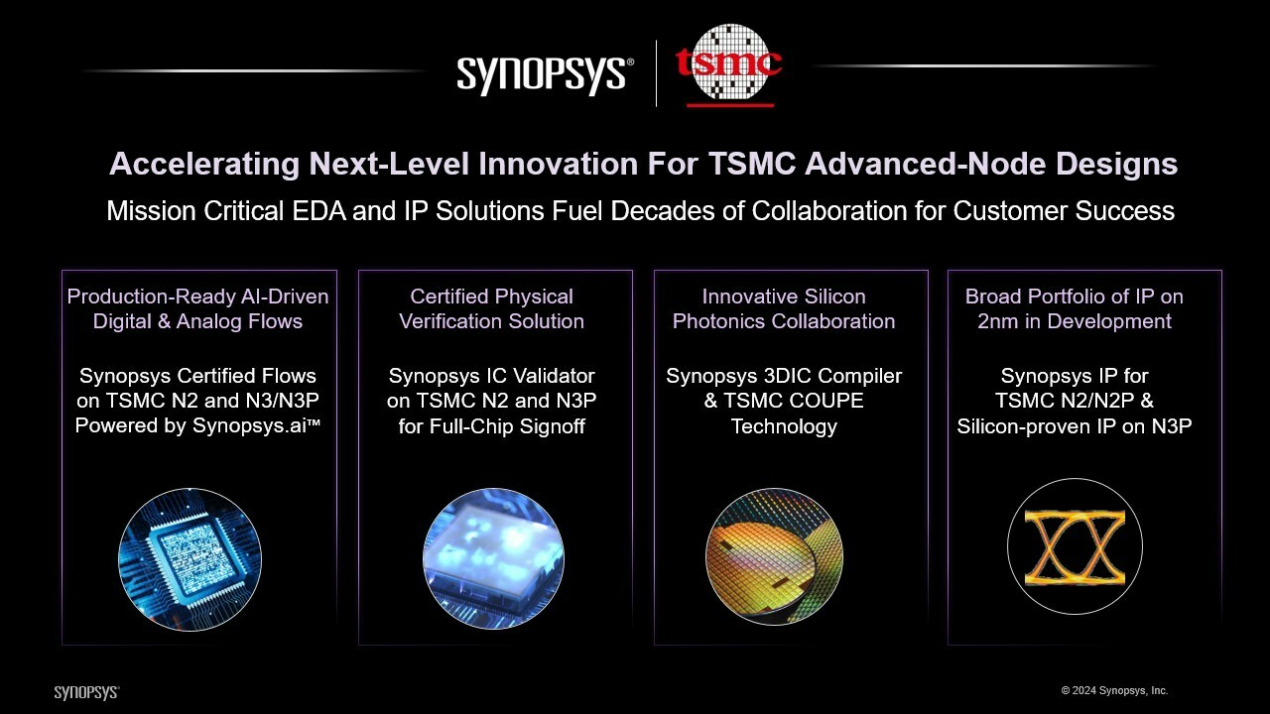

● 由Synopsys.ai™ EDA套件赋能可投产的数字和模拟设计流程能够针对台积公司N3/N3P和N2工艺,助力实现芯片设计成功,并加速模拟设计迁移。

● 新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证,可加速全芯片物理签核。

● 新思科技3DIC Compiler和光子集成电路(PIC)解决方案与台积公司COUPE技术强强结合,在硅光子技术领域开展合作,能够进一步提高人工智能(AI)和多裸晶(Multi-Die)设计的系统性能。

● 新思科技针对台积公司N2/N2P工艺开发了广泛的基础和接口IP产品组合,以及针对台积公司N3P工艺经过硅验证的IP,可缩短设计时间并降低集成风险。

新思科技(Synopsys, Inc.)近日宣布,携手台积公司在先进工艺节点设计开展广泛的EDA和IP合作,这些合作成果已应用于一系列人工智能(AI)、高性能计算(HPC)和移动设计中。其中双方的最新合作是共同优化的光子集成电路(PIC)流程,使硅光子技术应用赋能更高功率、性能和晶体管密度的需求。值得一提的是,业界高度认可新思科技的数字和模拟设计流程,这些流程可用于台积公司N3/N3P和N2工艺技术的 生产。目前,两家公司正在共同开发包括新思科技DSO.ai™在内的下一代AI驱动型芯片设计流程,以优化设计并提高芯片设计生产力。新思科技还针对台积公司N2/N2P工艺开发了广泛的基础和接口IP产品组合。此外,新思科技、是德科技(Keysight)与Ansys共同推出了全新的集成射频(RF)设计迁移流程,以实现从台积公司N16工艺节点至N6RF+工艺节点的迁移。

新思科技EDA事业部战略与产品管理副总裁Sanjay Bali表示:“新思科技在可投产的EDA流程和支持3Dblox标准的3DIC Compiler光子集成方面取得的先进成果,结合我们广泛的IP产品组合,让我们与台积公司能够帮助开发者基于台积公司先进工艺加速下一代芯片设计创新。我们与台积公司数十年的紧密合作建立了深厚的信任,持续为业界提供了至关重要的EDA和IP解决方案,帮助合作伙伴实现跨工艺节点的快速设计迁移,从而大幅提高结果质量和生产力。”

台积公司设计基础设施管理部负责人Dan Kochpatcharin表示:“我们与新思科技等开放创新平台(OIP)生态系统合作伙伴紧密合作,赋能合作伙伴更好地应对从埃米级器件到复杂的多裸晶芯片系统等一系列高性能计算设计领域中极具挑战的芯片设计需求,始终屹立于创新的最前沿。台积公司与新思科技将继续携手助力开发者基于台积公司的先进工艺节点实现下一代差异化设计,并加快成果转化速度。”

针对先进工艺节点的经认证数字和模拟设计流程

新思科技针对台积公司N3P和N2工艺的可投产数字和模拟设计流程,已被应用于一系列AI、HPC和移动设计领域。该AI驱动的模拟设计迁移流程可实现工艺节点间的快速迁移,在新思科技已有的针对台积公司N4P至N3E和N3E至N2工艺节点迁移的设计流程基础上,新增了用于从台积公司N5至N3E工艺节点的迁移流程。

此外,可互操作工艺设计套件(iPDK)和新思科技IC Validator™物理验证运行集已可供开发者使用,帮助芯片开发团队高效地将设计迁移至台积公司的先进工艺技术。新思科技IC Validator支持全芯片物理签核,以应对日益复杂的物理验证规则。新思科技IC Validator现已通过台积公司N2和N3P工艺技术认证。

借助光子集成电路加速多裸晶设计的数据传输

AI训练所需的海量数据处理要求低时延、高能效和高带宽的互连,这也推动了采用硅光子技术的光学收发器和近/共封装光学器件的应用。新思科技和台积公司正在面向台积公司的紧凑型通用光子引擎(COUPE)技术开发端到端多裸晶电子和光子流程解决方案,以提升系统性能和功能。该流程包括利用新思科技OptoCompiler™进行光子集成电路设计,以及利用新思科技3DIC Compiler和Ansys多物理场分析技术进行电子集成电路(EIC)的集成。

利用针对N2和N2P工艺的广泛IP组合加快产品上市速度

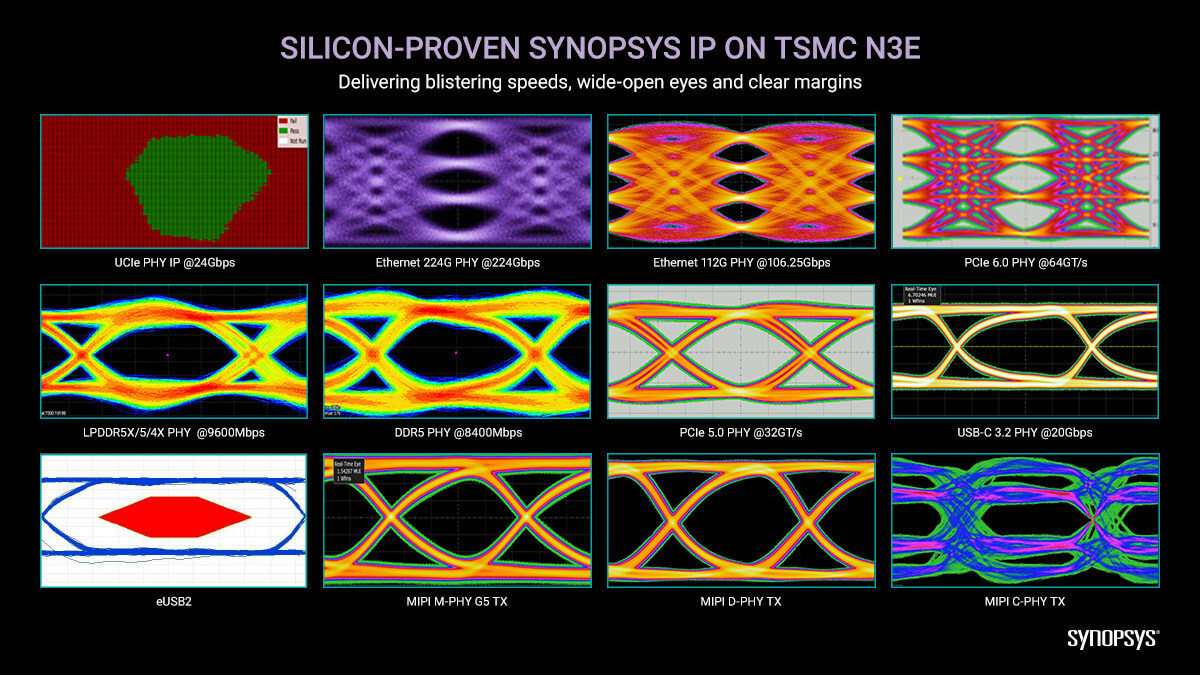

目前,新思科技正在针对台积公司的N2和N2P工艺技术开发广泛的基础和接口IP组合,以助力复杂的AI、HPC和移动SoC应用加速实现流片成功。基于N2和N2P工艺节点的高质量PHY IP,包括UCIe、HBM4/3e、3DIO、PCIe 7.x/6.x、MIPI C/D-PHY和M-PHY、USB、DDR5 MR-DIMM和LPDDR6/5x,开发者能够受益于台积公司先进工艺节点上的PPA改进。此外,新思科技还针对台积公司N3P工艺技术提供经过硅验证的基础和接口IP组合,包括224G以太网、UCIe、MIPI C/D-PHY和M-PHY、USB/DisplayPort和eUSB2、LPDDR5x、DDR5和PCIe 6.x,以及正在开发中的DDR5 MR-DIMM。新思科技针对台积公司先进工艺节点的IP已被数十家业内领先公司采用,以加快其开发进度。

关键词: 新思科技 台积公司 3DIC Compiler 光子集成电路

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

-

-

-

-

-

-

-

国际视野 2024-04-17