做信号链,你需要了解的高速信号知识(三)

_____

高速总线升级迭代的矛盾在于,消费者对性能的需求驱动着信号速率成倍的增长,消费者对便捷性的需求使得传输线无法缩短,消费者对低成本的追求要求PCB板材和传输线不能太贵,这就导致ISI抖动变得越来越严重。均衡(Equalization)就是为了应对ISI抖动,而被广泛应用的黑科技。既然ISI抖动的根源,是传输链路对不同频率信号损耗的差异,均衡就是要想办法补偿掉这个差异,让不同频率信号的幅度都能保持均匀。

根据均衡技术所使用的位置,一般分为发送端均衡(Tx EQ)和接收端均衡(Rx EQ)。

发送端均衡一般采用前向均衡(FFE, Feed Forward Equalization) 技术,用一组移位寄存器配合乘法器和加法器,根据当前bit位r(n)受到前若干bits r(n-1) 、r(n-2) 、r(n-3)…的影响,来修正r(n)的电压值。典型的表达式是:

e(n)=r(n)*k1+r(n-1)*k2+…

这个表达式有N项,就称之为N阶FFE,代表当前bit的电平,受到自身及前(N-1) bits的影响。在高速串行中应用最广泛的“预加重/去加重“(Pre/De-emphasis)技术,就是一个二阶的FFE,它会根据当前bit和前1 bit的逻辑状态,来调整当前bit的电平。

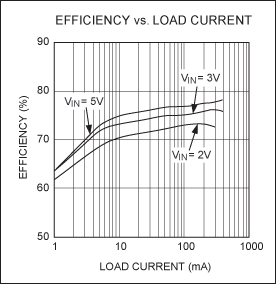

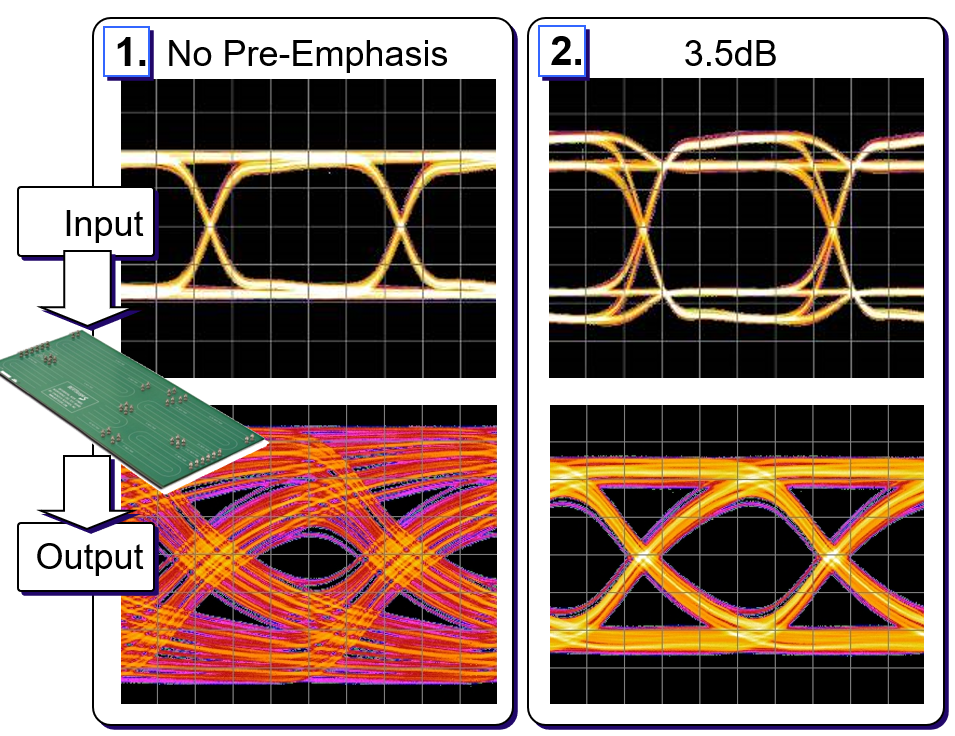

我们来看一个Pre-emphasis的真实案例。当发送端的信号不做任何处理时,发送端眼图是很完美的;一旦信号经过长背板传输之后,严重的ISI抖动会导致眼图几乎闭合(例1)。当发送端增加3.5dB预加重时,会将频率较高的跳变沿信号(Transition Bits,指的是与前一bit逻辑状态不同的bit,如01码型中的1,或110码型中的0等) 的幅度增强3.5dB。这些预先的增强会部分抵消长背板的损耗,从而不同码型的电平在到达接收端时基本相等,ISI抖动就大幅降低了。接收端的眼图无论是眼高眼宽,还是抖动,都有非常明显的改善(例2)。

图20 发送端均衡对眼图的影响

如果说发送端均衡是未雨绸缪,那么接收端均衡就是亡羊补牢。当ISI 抖动已经传递到了接收端,接收端应该如何进行均衡,尝试得到更好的眼图呢?接收端均衡一般采用CTLE(连续时间线性均衡)或DFE(负反馈均衡),或二者结合的方式,来降低数据的ISI抖动。

DFE均衡和FFE类似,不同的是DFE有负反馈调节功能。通过负反馈,可以自适应均衡系数,以达到最佳的均衡效果。同时, DFE不仅能消除ISI抖动,对于通道间的串扰也能提供一定的补偿效果,对于信号完整性的提升用处很大。

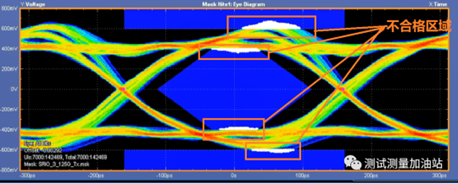

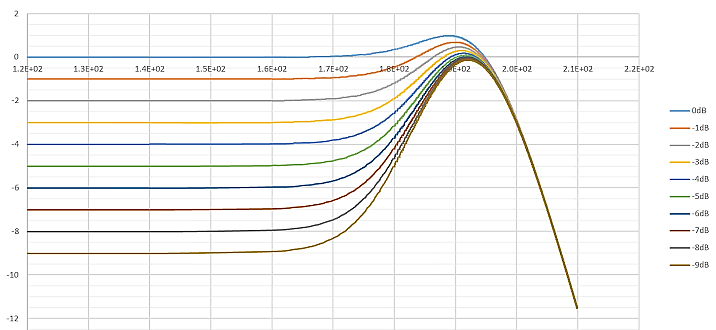

CTLE 的实现方法和FIR滤波器有点像,实现的是一个近似带通滤波器的效果。下图是一组典型的CTLE滤波器,低频衰减大,而高频衰减小。这个滤波曲线,和传输链路的损耗正好形成互补(传输链路插入损耗是低频衰减小,而高频衰减大)。在接收端,实现了不同频率间均匀的总体损耗,从而降低了ISI抖动。CTLE和DFE/FFE不同,它不依赖参考时钟,在连续时间域上对信号进行均衡;而DFE/FFE是数字域上的均衡,必须要先有参考时钟,来区分不同的bit,才能进行均衡。接收端常常使用CTLE和DFE的组合,先用CTLE打开近乎闭合的眼图,恢复出时钟,再用DFE进一步均衡补偿。

图21 典型的CTLE均衡类似于带通滤波器

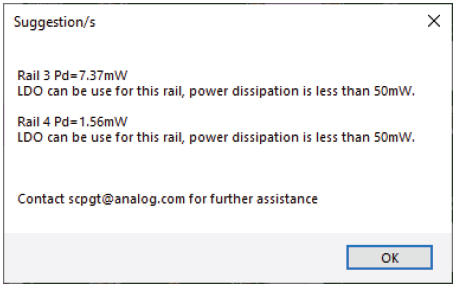

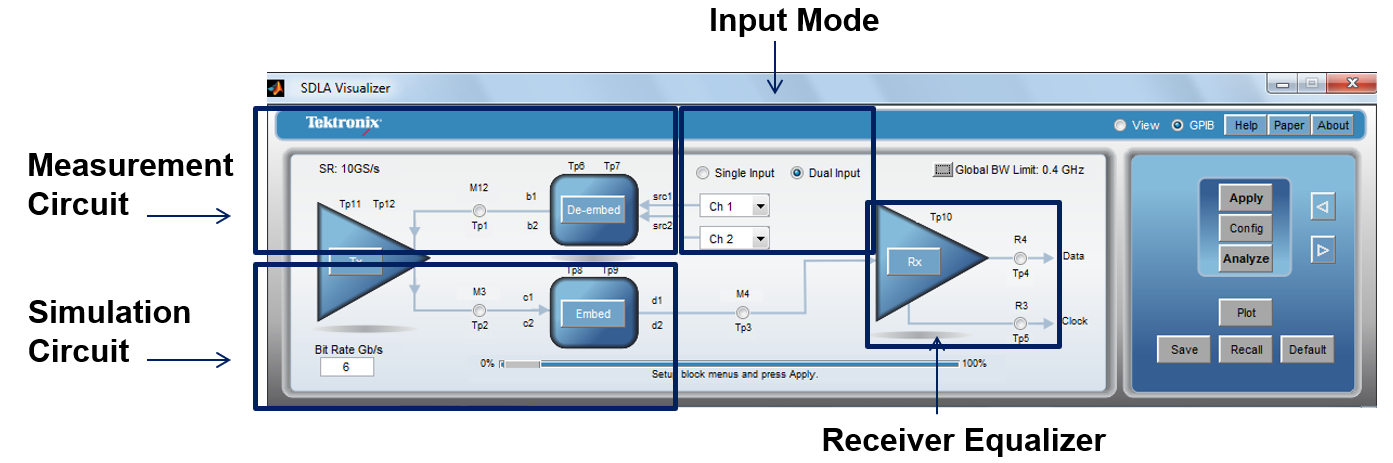

设计工程师为了解决ISI问题,常常需要在链路损耗和均衡技术之间做出综合考虑。泰克的SDLA软件可以模拟发送端的Tx EQ和接收端的Rx EQ,还能模拟传输链路的不同损耗。

图22 SDLA软件支持发送端、接收端均衡,以及链路嵌入/去嵌模拟

让你在产品设计的初期,就能预估链路的ISI抖动,探索和尝试最佳的均衡组合以降低ISI抖动,大幅减少产品研发的时间。

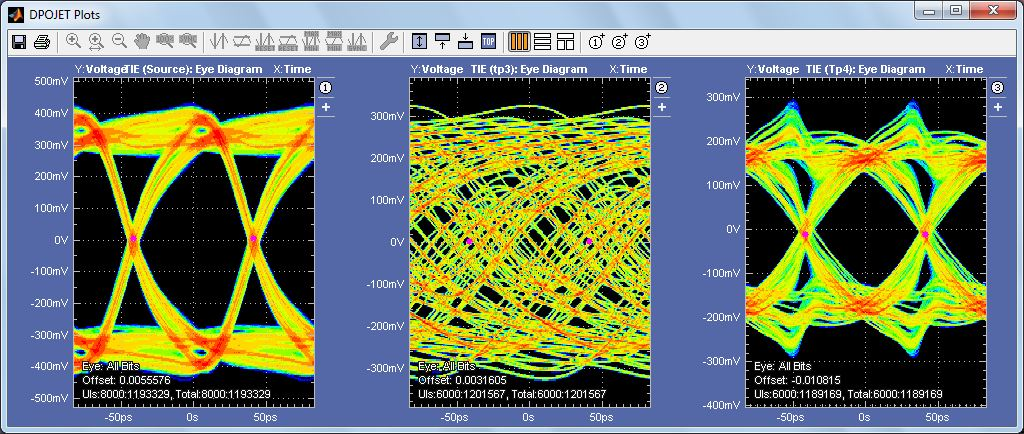

图23 发送端眼图,通过SDLA通道嵌入得到的接收端眼图,通过SDLA接收机均衡得到的最终眼图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码