使用CD4027的JK Flip Flop

CD4027 是一种 JK 触发器,一般用于数据存储。集成电路中包含两个相似或相等的 JK 触发器。集成电路中的每对 JK 触发器都有 J、K、设置、复位和时钟引脚,以及两个互补的输出端。JK 触发器可用于语音寄存器、计数器等应用,也可用作控制电路。

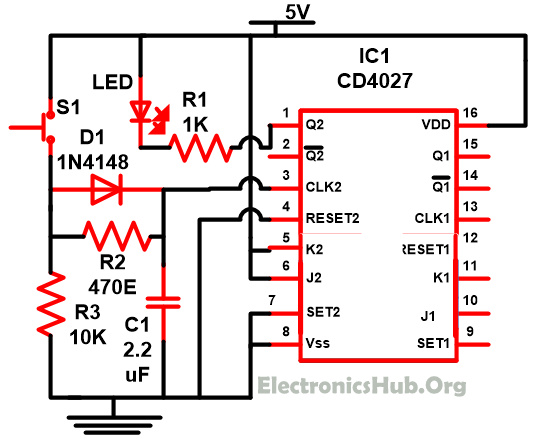

使用 CD4027 的 JK 触发器电路图:

电路元件:

集成电路

CD4027

电阻器

R1(1K)

R2(470E)

R3(10K)

C1(2.2uf)

S1

发光二极管

D1(1N4148)

使用 CD4027 的 JK 触发器电路说明:

CD4027 是一个 JK 触发器,主从模式,用于切换模式。集成电路通过从一个或多个输入端提供控制输入来改变信号,并在一个或多个输出端获得输出。输出值不仅取决于当前的输入状态,还取决于当前的状态(也取决于先前的状态)。计算机内部的存储电路主要使用触发器。

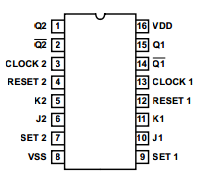

JK 触发器有四个输入引脚,分别为 J 和 K,以及设置引脚和复位引脚,输出引脚为 Q 和 Q¯。Q 和 Q¯ 的值是相反的,即 Q 的值越高,Q¯ 的值就越低,两个终端的输出取决于输入的配置方式。

CD4027 中的 IC 引脚配置

输入端 J 和 K 的逻辑电平以及内部控制用于控制触发器的阶段。在每个正向循环中,状态都会发生变化。其中的设置和复位引脚不依赖于时钟脉冲,当任何一个输入终端发出高电平信号时,设置和复位引脚就会启动。

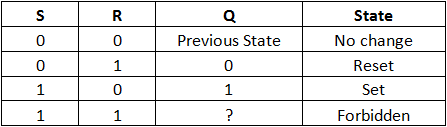

所述电路在开关脉冲的最前沿触发,即开关按下一次,其输出就改变一次。如电路所示,输入端 J 和 K 都设置为高电平,这意味着每次正负转换时,时钟脉冲都在高电平和低电平之间波动。触发器的这种状态称为禁止状态,借助下面的真值表可以验证这些条件。

使用 CD4027 的 JK 触发器的工作原理

一旦按下开关,集成电路的输入端将获得一个小的时钟脉冲,其结果是引脚 1 输出变为高电平。直到接收到第二个脉冲,输出仍为高电平。与输出端相连的负载或指示灯启动。当第二个时钟脉冲到达引脚 3 时,集成电路输出变为低电平,LED 或与其相连的负载变为关闭。

该电路在按下开关时工作,但如果要断开电路,只需交换开关和电阻的位置即可。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码