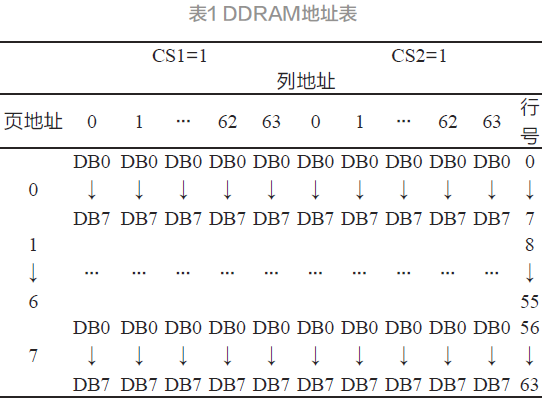

三维封装DDR2存储器VD2D4G72XB191XX3U6测试

编者按:DDR2 SDRAM具有速度快、价格便宜、容量大的特点,应用非常广泛。通过采用三维封装技术将5片数据位宽为16 bits的DDR2 SDRAM芯片封装成一个存储模块VD2D4G72XB191XX3U6,在不额外占用PCB面积的情况下,提高了存储容量,并将位宽扩展到72 bits。

摘要:与其它存储器相比DDR2 SDRAM操作较为复杂,封装成一个位宽72bit的模块后,测试难度进一步增加,针对这一问题,本文提出了基于Magnum 2测试系统的DDR2SDRAM存储模块VD2D4G72XB191XX3U6的测试方法,对直流参数、交流参数以及功能进行了测试,论述了测试的关键技术。

DDR2 SDRAM 以高速、大容量著称,但是缺点也很明显,操作复杂、掉电丢失数据、需定时刷新,这给测试带来了不小的难度。尤其是在航空航天领域,对小型化要求比较高,产生了一种利用三维封装的技术将多片芯片垂直堆叠制作成一个存储模块,这样在不占用额外PCB 面积的情况下增大了容量。VD2D4G72XB191XX3U6 就是利用该技术制作而成,在增加容量的同时,将数据位宽从16 bit 扩展到72 bit,满足了用户的特殊要求。

同时为了应对航空航天对可靠的特别要求,需要对DDR2 SDRAM 进行覆盖性测试[1],即对芯片内部每个存储单元进行不同pattern 的读写测试,测试验证的同时还需要兼顾时间效益,经济效益。本文介绍了基于MagnumII 存储器测试系统对DDR2 SDRAM 存储模块VD2D4G72XB191XX3U6 的直流参数、交流参数和功能覆盖性测试的方案。

1 MagnumII 存储器测试系统[2]

Magnum II 存储器测试系统是Teradyne 公司生产的存储器专用测试系统,每个Site Assembly Board 具有128 数字通道,每个测试通道均有独立的时序和电平。Magnum II 测试系统有着强大的算法向量生成器APG(Algorithmic Pattern Generator),最大能够支持24 bit行选、24 bit 列选、36 bit 数据位宽和18 个片选。

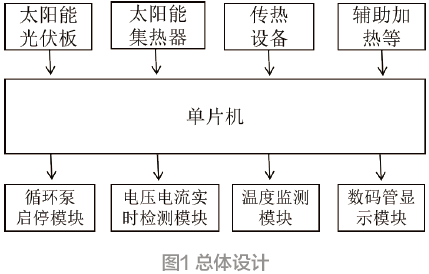

2 VD2D4G72XB191XX3U6存储器结构

VD2D4G72XB191XX3U6 的拓扑结构如图1 所示,内部采用5 片ISSI 公司生产的IS43DR16640B 芯片,单颗芯片容量为64 M×16 bits,分3 层进行叠装,通过灌封、切割、金属化、激光雕刻等工序生产而成。内部5 个芯片的片选(#CE)、地址总线[A12:0] 合并引出,数据总线DQ[71:0] 并联引出,将5 片数据宽度为16 bit的芯片扩展成为72 bits 的存储模块,其主要特性如下:

● 总容量:4G bit;

● 工作电压:1.8 V±0.1 V;

● 数据宽度:72 bit;

● 时钟频率:333 MHz;

● BL:4,8;

● 刷新周期:64 ms;

● 封装形式:SOP70。

3 初始化

DDR2 SDRAM 产品在上电使用前需进行初始化,并对模式寄存器(Mode Register)进行配置,确定所需要的突发长度(Burst Length)、突发类型(Burst Type)、CAS 延时等。初始化时需遵循以下步骤[3]:

Step1:上电后保持CKE 和ODT 低电平,VDD 电压上升时间应小于200 ms;

Step2:保持稳定时钟;

Step3:电压稳定不少于200 us 后,CKE 才能置为逻辑高电平,同时发送NOP 或Deselect 命令;

Step4: 等待400ns, 等待时只能发送NOP或Deselect 命令,发送Precharge All 命令;

Step5:配置EMR2;

Step6:配置EMR3;

Step7:配置EMR 使能DLL;

Step8:配置MR,复位DLL;

Step9:发送Precharge All 命令;

Step10:发送两次以上的Auto-Refresh 命令;

Step11:配置MRS,A8 = 0;

Step12:等待200 个周期,执行OCD 校准;

Step13:DDR2 SDRAM 产品初始化完成。

具体时序见下图:

图2 初始化和配置模式寄存器时序

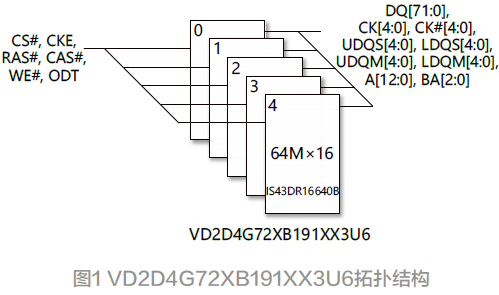

模式寄存器(MR)的配置参数见图3。

图3 模式寄存器(MR)配置参数

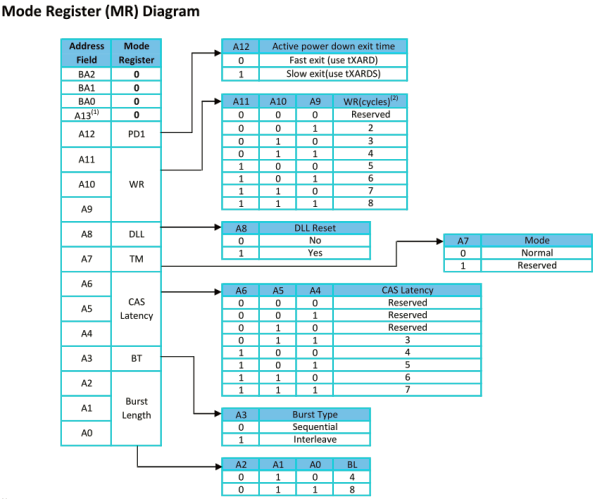

扩展模式寄存器1(EMR1)的配置参数见图4 。

图4 扩展模式寄存器1(EMR1)

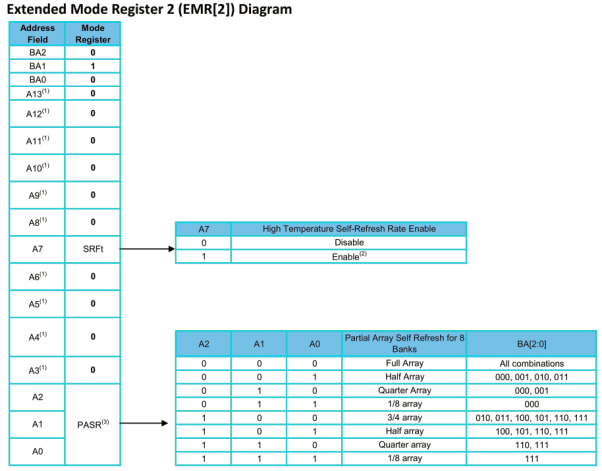

扩展模式寄存器2(EMR2)的配置参数见图5。

图5 扩展模式寄存器2(EMR2)

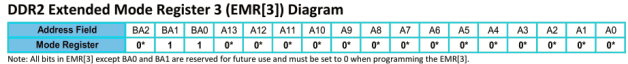

扩展模式寄存器3(EMR3)的配置参数见图6。

图6 扩展模式寄存器3(EMR3)

4 直流参数测试

直流参数测试主要包括:开/ 短路测试(O/S);连通性测试(continuity),通过测试每个引脚内部保护二极管的管压降是否正常来判断引脚的连通性是否正常,一般来说测试时必须先进行连通性测试;输入漏电流(ILIH/ILIL)和输出漏电流(ILOH/ILOL)是在电源电压为0 时,输入引脚和输出引脚施加高电平和低电平的电流,该电流反映的是引脚之间的直流阻抗;IDD 测试的是芯片工作时或休眠时消耗的电流,该电流反映的是芯片的功耗;输出高/ 低电平测试(VOH/VOL)测试的是DQ 引脚在输出高电平和输出低电平时的电压大小。

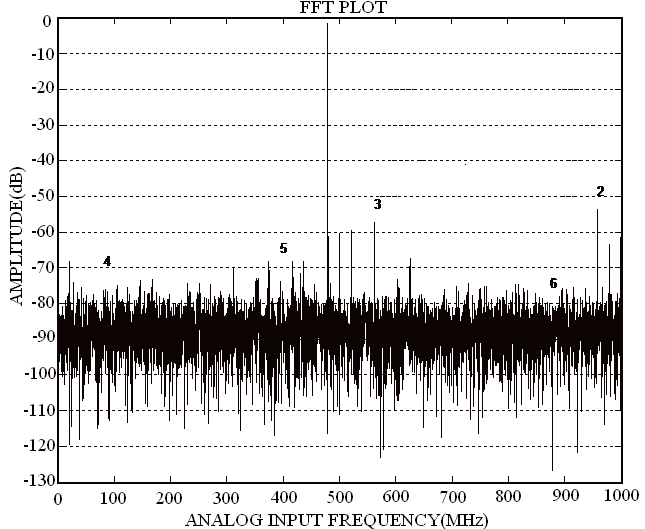

5 交流参数测试

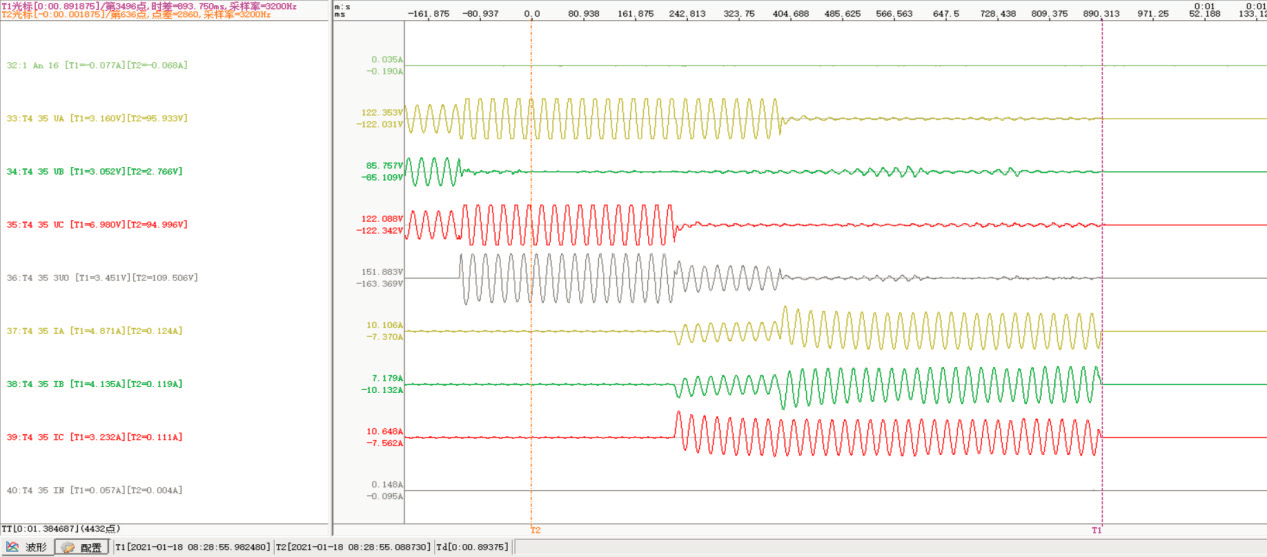

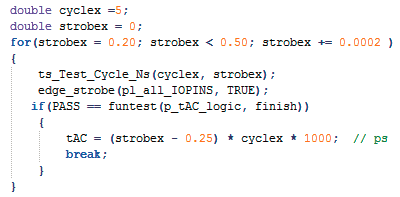

交流参数表征的是芯片的工作性能,一般用搜索法来测试交流参数,下面以在Magnum 2 测试系统上测试tAC参数为例来介绍测试机如何进行交流参数的测试,tAC时钟上升沿到数据输出延时(Address to Output Delay),该参数越小则产品响应速度越快。

搜索法的具体思路为假设t0时刻地址有效,随后在t0+tSTEP进行读数据,如果读取成功,则tAC=t0+tSTEP,如果读取失败则在t0+2tSTEP时读取数据,如此循环直到读取成功为止。搜索法比较简单,tSTEP的大小决定了测试的精度,如果tSTEP设置的比较小,那么测试耗用的时间势必较长。

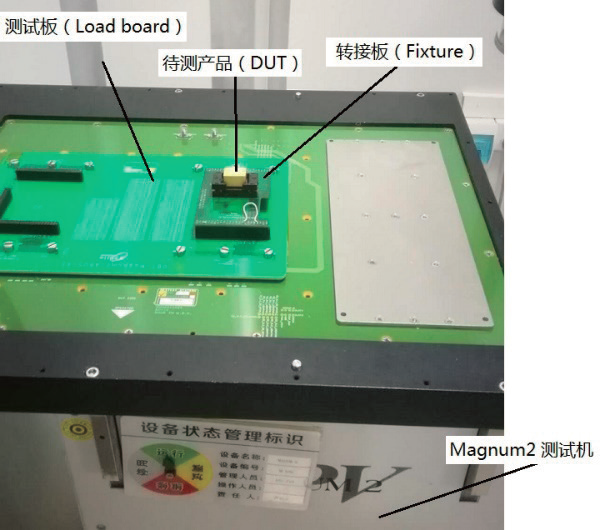

测试前现将芯片装载到测试夹具上,然后将夹具安装到测试系统的测试板(Loadboard)上,见图7。Magnum 2 的测试软件是在VC 下编写的,文件pin_assignments.cpp 中定义芯片的各引脚,并定义引脚与Magnum 2 系统测试通道的连接关系,这样就实现了芯片与测试系统的连接。在文件voltage.cpp 中定义电源电压、输入高低电平的电压值以及DQ 引脚的负载电流,文件timing.cpp 中定义的是各引脚在每个周期(Cycle)中的波形,文件pin_scramble.cpp 中定义的是各引脚与向量生成器(APG)的连接关系,以上就完成了交流测试前的配置工作。

图7 Magnum 2测试系统

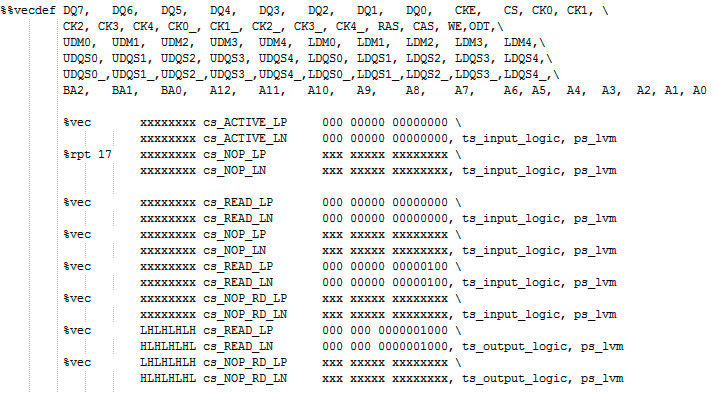

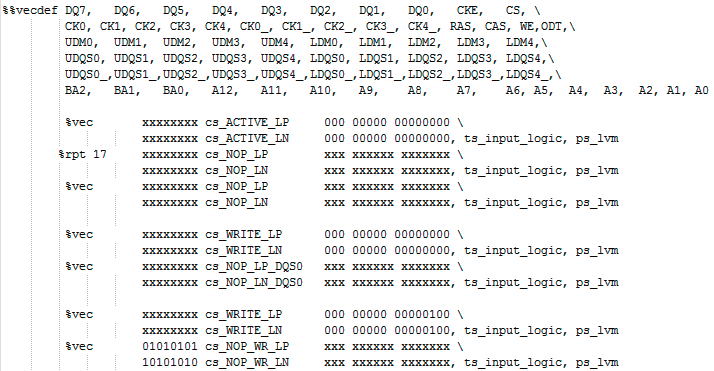

芯片的功能是逻辑向量(logic pattern)来实现的,在VC6.0 下向量代码如下图所示。

图8 读向量代码

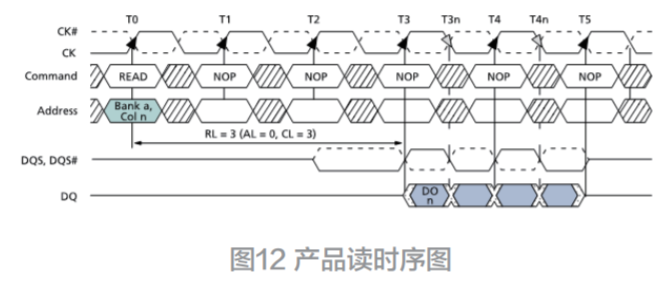

不同于EEPROM、SRAM、MRAM 器件,DDR2SDRAM 器件在进行读写操作前需先对目标行(Row)进行激活(Active)。激活完成后发送读命令和地址,等待CAS 延迟后才能读取数据,读时序图见图12。

图9 为搜索法的测试代码,该代码中设置测试周期为200 ns,搜索步长为1 ps,搜索范围为1 ns~2.5 ns,如果测试通过则停止搜索。搜索法简单方便,是一种常用的交流参数测试方法,如果精度要求不高,则步长可以适当加长以提高测试效率。

图9 搜索法代码

6 功能测试

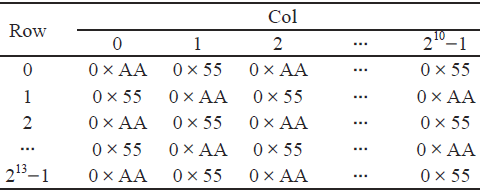

存储器的功能算法有多种,如全0、全1、棋盘格、反棋盘格、累加数、march 等等,不同的算法检测的故障不同,测试的覆盖性不同,耗用的时间也不同,可以根据测试的目的来选择。

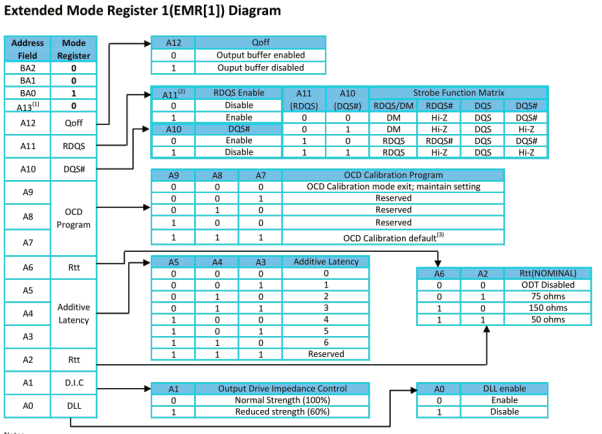

以棋盘格算法为例对产品进行功能测试,表1 为棋盘格算法向量表。由表1 可知,每个存储单元存储的数据与周围存储单元存储的数据互为反码,因此在读写时,每个周期(cycle)DQ 管脚的电平都改变一次。

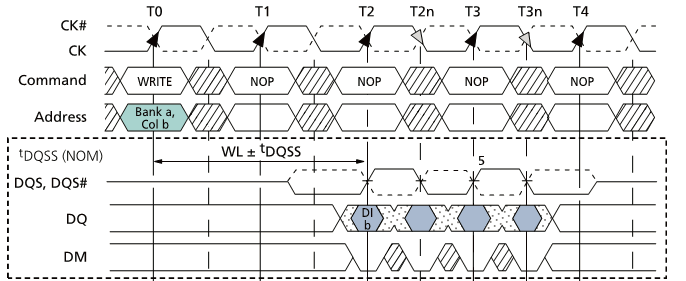

存储在进行操作时,应该严格按照时序图来进行。图10 为产品的写时序图,命令、地址和数据均在时钟上升沿被锁存。

表1 棋盘格向量

图10 写时序图

写操作的向量代码如图11 所示,与图8 中的读操作类似,在进行写操作前,需要先对目标行进行激活操作,并等待tRCD 时间后才能进行写操作。

图11 写向量代码

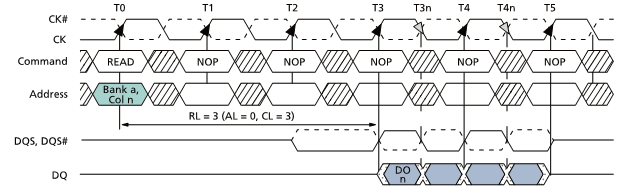

图12为产品的读时序图,读向量代码见图8 。

图12 产品读时序图

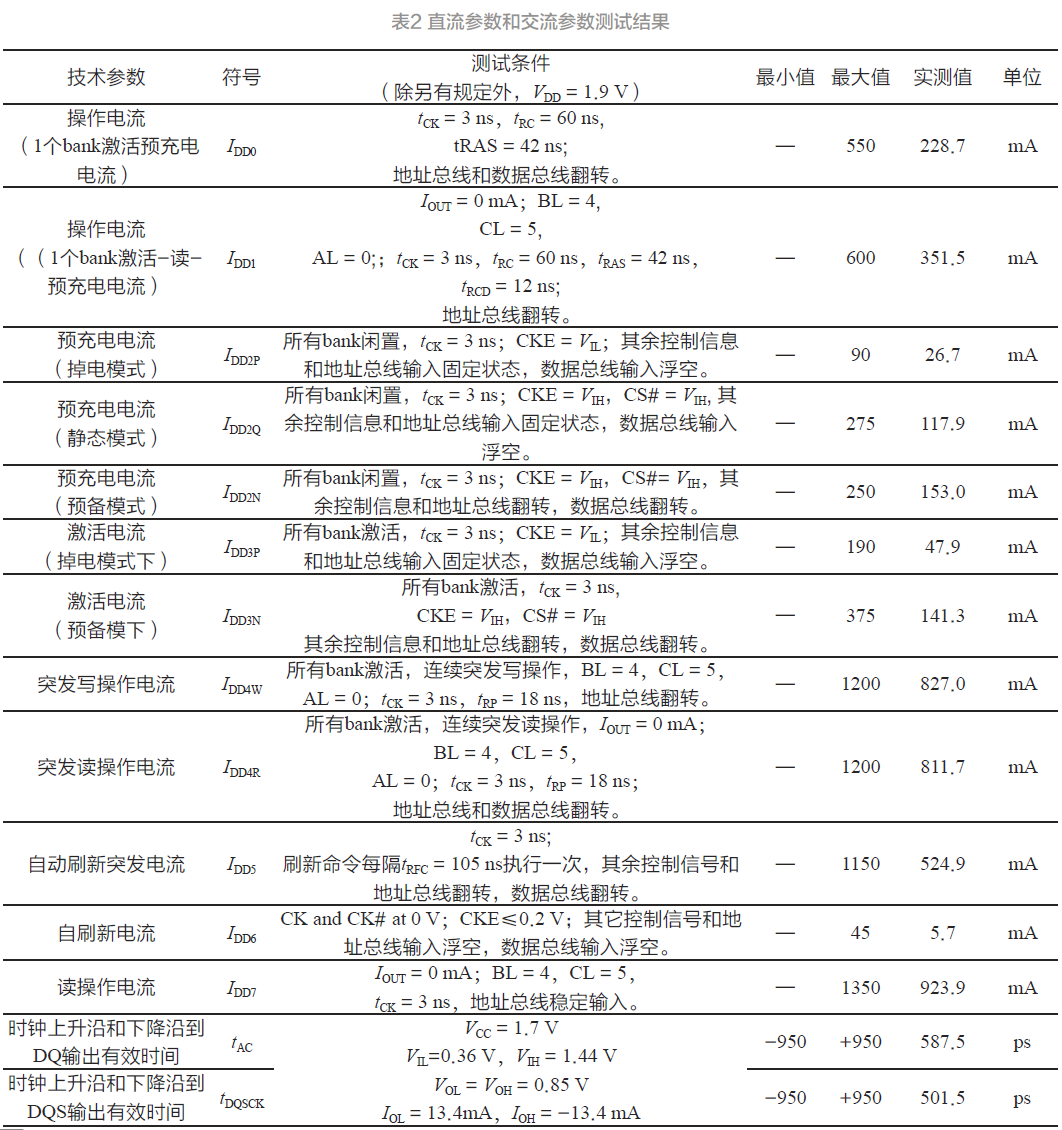

7 测试结果

表2 所示为产品的参数标准以及实测结果,由表2的测试结果可知,在规定的测试条件下实测结果均在标准范围内,证明了测试方法的正确性。

8 结论

本文介绍了Magnum 2 测试系统和产品存储器,提出了一种测试产品存储器的测试方法以及测试代码的编写,并对该存储器的连通性、直流参数、交流参数和功能进行了实测,验证了测试正确性。

参考文献:

[1] 郑小牧.SDRAM存储器测试的实现与优化[D].北京:中国科学院大学,2013.

[2] NEXTEST.Magnum 2 Test System PV Maintenance Manual[R].

[3] ISSI Datasheet for 1Gb DDR2 SDRAM IS43DR16640B,Rev.G[S].

(本文来源于必威娱乐平台 杂志2022年5月期)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码