深度解读基于USB接口VSAT基带数据采集系统设计

0 引言

在众多的卫星通信系统中,VSAT(甚小口径卫星终端)卫星通信系统由于具有众多特点,近年来发展很快,特别在专业通信网领域存在广阔的市场,利用此系统进行通信具有灵活性强、可靠性高、成本低、使用方便及小站可直接装在用户端等特点,并且VSAT用户数据终端可直与计算机联网,完成数据传递、文件交换、图像传输等通信任务,从而摆脱了远距离通信地面中继站的问题,因此,此系统广泛用于石油、银行、铁路、民航、军事等行业。

在VSAT系统中,用户终端通常是由数字卫星接收机和计算机终端组成,数字卫星接收机包括下变频器、解码器、FEC(前向纠错),解复用器、数字基带处理器和频率合成器等部分,接收机输出的数据一般通过RS-232,RS-422/449以1.2kbit/s-64kbit/s的数据率交给计算机完成应用处理,有些高速卫星数据接收设备解调以后,数据通过额外高速数据卡送入计算机。这种传统的数据卡不仅安装麻烦,且易受机箱内环境的干扰,特别是这种卡通常只能接收单路数据,受计算机插槽数量和地址,中断资源的限制,不可能挂接多个设备,因此,资源浪费尤其严重。

针对这种情况,本文结合卫星接收设备数据采集的实际需要,设计了一种基于USB(通用串行总线)接口的USAT基带数据采集系统,该系统通过对USB接口控制逻辑的合理设计和芯片内部FIFO的有效运用,充分应用了CPLD(复杂可编程逻辑器件)的灵活性,仅采用单片USB接口控制芯片就实现了对多路多速率数字信号的实时采集,这与以往采用USB集线器来实现对多路多速率数字信号采集的系统相比,具有成本低、实现方便等优点。

该系统最多可同时采集8路数字信号,单路最高速率可达2Mbit/s,系统用于控制的CPLD采用Altera公司的EPM7128SLC84;USB接口控制芯片采用Cypress公司EZ-USB FX2系列CY7C68013。

1 系统原理

1.1 USB简介

USB(通用串行总线)是一种应用在PC领域的新型接口技术,支持在主机与各种即插即用外设之间进行数据传输,它由主机预定传输数据的标准协议,在总线上的各种设备分享USB总线带宽,它的主要优点是:数据传输速率明显快于一般的串口,支持控制传输、中断传输、块传输的和同步传输4种传输方式,以满足不同外设的需要,最多可连接127个外设,支持热拔插和即插即用,占用的系统资源少(只占用1个IRP(I/O请求包));无总线竞争等。USB总线技术的提出就是想利用单一的总线技术来满足多种应用领域的需要,USB1.1协议支持低速1.5Mbit/s和全速12Mbit/s两种传输速度。2000年发布了USB2.0协议,它向下兼容USB1.1协议,但在USB1.1的基础上有了质的提高,其理论传输速度可到480Mbit/s。

1.2 系统结构

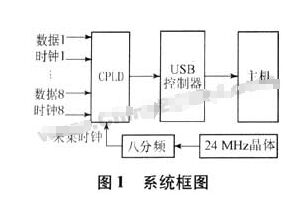

该系统总体框架分采集控制部分、USB接口控制部分和主机3部分,系统框图如图1所示。

外部输入的8路信号中时钟、数据均为TTL电平,采集用的统一时钟为3M赫兹,是由USB控制芯片的外部时钟经八分频得到的。

系统的工作过程如下:每路信号在CPLD的控制下,按采集时钟的统一节拍,各路信号的数据和时钟都被采集进CPLD。在CPLD内,先进行各路信号的时钟上升沿检测,如检测到时钟上升沿,则在相应路数的标志位置1,这表明此时采到的数据有效,若没检测到时钟上升沿,则在相应路数地标志位置0,表明此时采集的数据无效,这样形成的各路信号数据,再加上各路信号数据是否有效的标志,形成2字节的数据送入USB控制芯片的FIFO中,数据进入USB控制芯片后,通过USB接口将数据传输到主机,数据在主机中用软件进行处理,按照各路信号数据是否有效的标志位,将有效数据取出,组合成各路数据。

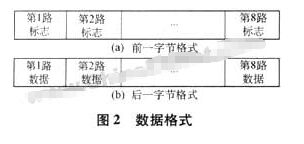

数据送入主机时的格式如图2所示,前一字节为各路信号数据是否有效的标志,紧跟着的字节为各路信号的实际数据,采用这种特殊的数据格式,以区分各路信号,便于采用统一的时钟来实现对多路多速率数字信号的实时采集,从而减少了很多硬件电路,降低了成本和复杂性,实现更为方便,这也是本系统的一个创新点。

2 硬件构成

2.1 EZ-USB FX2(CY7C68013)芯片

CY7C68013属于Cypress公司的FX2系列产品,它提供了对USB2.0的完整解决方案,该芯片虽然采用低价的8051单片机,但仍然能获得很高的速度,主要包括USB2.0收发器、SIE(串行接口引擎)、增强型8051处理器、8.5KB的片上RAM,4KB FIFO存储器、I/O口、数据总线、地址总线和GPIF(通用可编程接口)。

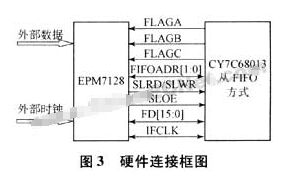

CY7C68013与外设有可编程接口GPIE和从FIFO两种接口方式。可编程接口GPIF是主机方式,可以由软件设置读写控制波形,灵活性很大,几乎可以对任何8bit/16bit接口的控制器、存储器和总线进行数据的主动读写,使用非常灵活,从FIFO方式是从机方式,外部控制器可像对普通FIFO一样对FX2的多层缓冲FIFO进行读写。在本设计中为了方便控制,采用从FIFO方式。

2.2 CPLD芯片EPM7128SLC84

在本设计中,所用的CPLD采用Altera公司的EPM7128SLC84。它属于MAX7000系列,是Altera公司的基于第2代MAX结构的CPLD。它提供多达5000个可用门、128个宏单元,其引脚到引脚延时快达6ns。可以容纳各种独立的组合逻辑和时序逻辑功能,EPM7128S的优点是它基于E2PROM,可以通过JTAG口进行在线编辑,设计者可将设计内容从PC机上通过下载电缆和JTAG口对EPM7128S进行任意次修改,它有多达100个I/O引脚可供编程使用,方便系统扩展存储空间和外设。

本系统使用EPM7128S的主要功能是对各路信号的时钟上升沿进行检测,另外还需要完成一些控制功能,完成各路信号数据的合路,形成特定的数据格式,送入USB控制芯片的FIFO中。

2.3 硬件连接

根据系统对数据传输的速度和实时性的要求,配置CY7C6013的工作接口模式为从FIFO模式,硬件连接方式如图3所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码