基于DSP/CPLD的嵌入式仪表硬件平台

数字化、智能化是仪器仪表的发展方向之一,同时仪器仪表的数据采集速度越来越快,数据量越来越大,对数据处理时间的要求也越来越短,这就对仪器仪表的硬件平台提出了新的要求。目前很多简单智能仪表仍使用单片机来实现,单片机应用广泛,价格也很便宜,接口性能良好,容易实现人机接口,但单片机系统复杂,尤其是乘法运算速度慢,在运算量大的实时控制系统中很难有所作为。高端仪表的硬件平台通常使用嵌入式微机系统,但其成本比较高,也不宜产品的小型化。

总体方案

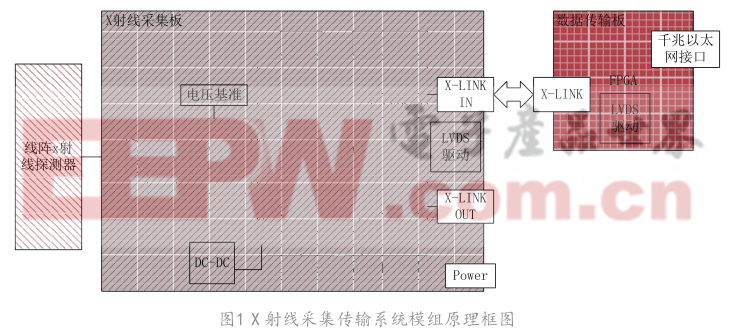

本文所要设计的是一种脱机型仪表硬件平台。平台应可以满足一般的数据采集的实时性要求,可以灵活的适用于多种不同的应用场合,可实现多种类型信号的采集和处理,结构小巧紧凑,便于现场处理,还能与PC机或其他设备进行通信和交换数据。对此,我们构建了基于DSP和CPLD技术的硬件平台。整个平台由三部分组成(图1)。

图1 总体框图

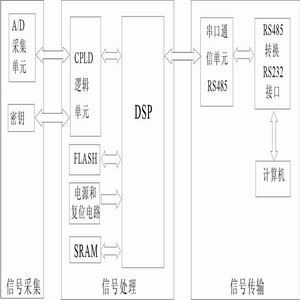

信号采集单元负责获取外部信息并将其转换为数字信号输出。在输入端,由于采用了灵活性很强的CPLD作为A/D与DSP之间的接口,使这个硬件平台可方便的适用于不同的应用场合。针对不同的传感器和应用需求,选择合适的A/D芯片。实验中,系统使用的是CMOS图像传感器OV7120,把图像转换为8位分辨率的数字图像。A/D输出的数据先经过CPLD预处理,DSP把CPLD作为一个端口读入数据,放到外扩的SRAM中。

信号处理单元是整个系统的核心,由TMS320C6712及其外围辅助电路构成,负责对采入的信号进行实时处理。DSP读入SRAM中的数据并进行相应的算法处理。系统中各模块间的通讯与逻辑控制由CPLD负责。

信号传输单元是DSP与PC机或其它系统实时通讯的中介。本系统中,DSP处理后的结果通过RS485总线远距离传输,最后通过RS485/RS232转换器送给PC机。工作流程框图如图2所示。

图2 程序流程图

硬件电路设计

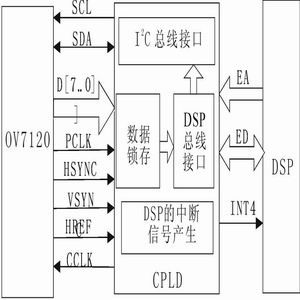

图像采集是OV7120和CPLD协同工作来实现的,CPLD为OV7120提供I2C接口来配置寄存器,同时提供CCLK时钟信号,并对图像数据锁存后传给DSP,图3是接口设计原理图。其中SCL、SDA为I2C控制线;CCLK为OV7120的输入时钟;PCLK、HSYNC、VSYNC分别为点频和行、场同步输出信号;D[70]为8位图像数据输出信号线;HREF是水平参考信号;INT4为DSP的中断。

图3 接口设计原理图

实 验

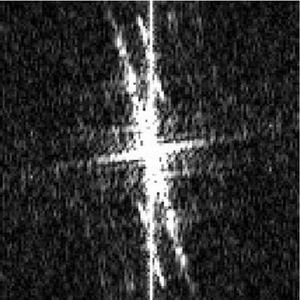

信号处理算法由DSP芯片实现,在实验中我们编写了二维FFT算法来验证平台的性能。二维FFT的实现流程如图4所示,算法由C语言编写。图5是实际采到的一幅图像,图6是提取256×256的图像并进行二维FFT运算后的结果。

图4 二维FFT流程图

图5 实际采得的一幅图像

图6二维FFT运算结果

实验表明该平台实现了图像采集和处理功能,图像采集速度约1帧/s,256×256的二维FFT算法的运行时间为960ms。但对于不像图像这么大的数据采集量,可以先将数据存放到内部RAM中的,系统的数据采集速度为12Mbyte/S,对于可以直接在内部运行的32×32的二维FFT算法的运行时间为5ms。

结 语

测试结果和实际应用说明,此平台具有较快的数据采集速度和较高的运算能力,能够完成实时数据的采集和处理,是一种体积小、重量轻、微功耗、低成本、处理速度快、可靠性高、便于升级的测试测量仪器平台,在仪器仪表领域具有着广阔的应用前景。平台所用DSP芯片为TMS320C6712,其主频目前只使用80MHz,运算速度不是很高,数据存储器为SRAM,读取速度也不是很快,如果将DSP升级为TMS320C6711(最高150MHz);并把数据存储器换为SDRAM,可以大大提高平台的运算速度。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码