基于FPGA和千兆以太网的线阵X射线图像采集传输系统

杨 地(电子科技大学 电子科学与工程学院,四川 成都 610054)

摘 要:基于FPGA核心与千兆以太网传输技术组建线阵x射线图像采集传输系统。FPGA芯片为核心控制,实现对X射线探测器控制、探测器信号积分时序、ADC采集时序控制、采集板间数据传输、千兆以太网数据传输控制。X射线探测器与采集板,采用菊花链数据传输结构方式以应对不同规模的场景。千兆以太网的传输确保了图像数据的实时、高速与精准度。

关键词:图像采集;x射线检测;FPGA;千兆以太网

0 引言

随着公共安全越来越受到公众的重视,X射线安检机已经成为地铁、汽车站、铁路和海关等人口密集交通场所出入等的必备安检设备。基于FPGA的X射线辐射图像采集与传输系统,利用X射线的穿透性扫描成像快速扫描行李箱、集装箱内物品,对枪支、易爆物和毒品等违禁物品进行快速甄别,保障公共安全与社会安宁 [1] 。X射线安检机由线阵X射线图像采集传输系统与上位机组成,本文主要研究线阵X射线图像采集与传输系统,其中包括探测板、采集板与数据板。采集系统采用基于闪烁晶体与硅光电二极管技术组合在一起的阵列式硅光电二极管探测传感器,Altera公司(注:已被Intel公司收购,更名为Intel公司)的Cyclone IV系列可编程门阵列为核心控制器,千兆以太网RGMII千兆媒体独立接口为与上位机通信媒介 [2] 。

1 X射线探测系统电路设计

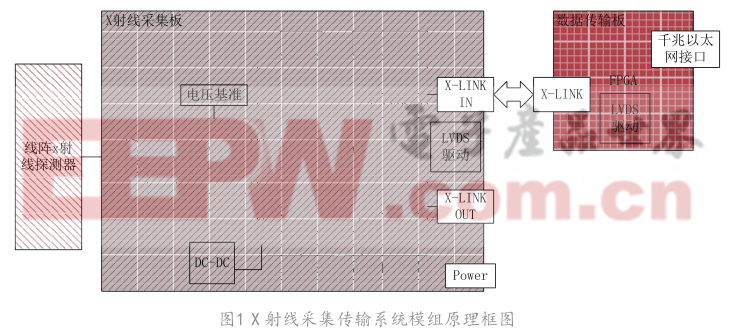

本文设计的X射线采集传输系统的硬件框图如图1所示。图像采集与传输系统的硬件包含三个部分,X射线探测器模块、FPGA数据采集模块和千兆以太网RGMII数据传输模块。

当 X 射线成像闪烁晶体(CsI)受X射线辐照后,将X射线转换为可见光,闪烁体贴合在阵列硅光电二极管表面,阵列硅光电二极管接收到可见光后转换为电流信号,再由前置集成放大器放大,积分转化为电压信号。放大器的灵敏度是由积分电路的反馈电容器定义。每路运放灵敏度设置可以从控制端口进行单独控制,放大后信号通过 A/D 转化成数字信号输送到采集板 FPGA 片内,FPGA 通过LVDS传输格式将数据传输给数据板。

采集板发送到数据板是通过端口直接进入数据板 FPGA进行信号处理。信号处理单元对每个像素数据的重新排序、数据校正、暗偏移和像素点的灵敏度差异等进行处理。最后数据板通过选定的数据接口(千兆以太网通讯端口) 将图像数据发送到系统PC上,与PC以千兆以太网接口连接。

1.1 线阵X 射线探测器模块

线阵X射线探测器模块由闪烁晶体(CsI)与硅光电二极管组成。闪烁晶体层受X射线辐照后,将X射线转换为可见光,闪烁体贴合在阵列硅光电二极管表面,阵列硅光电二极管接收到可见光后转换为电流信号。光电二极管阵列是 64 通道阵列;素间距为1.575 mm(双能探测器通道板是两个64路,共为 128 路),HE(高能量)和LE(低能量)。

本文采用的闪烁体X射线探测器滨松S11212,由64阵列二极管组成,像素间距为1.6 mm,阵列二极管采用背照式设计,具有更高的灵敏度一致性和更小的象元变化。该探测器的工作温度在-20℃~60℃,响应光线波长λ范围为340 nm~1100 nm,暗电流平均值为5pA,最大值不超过30 pA。

1.2 FPG A 数据采集模块

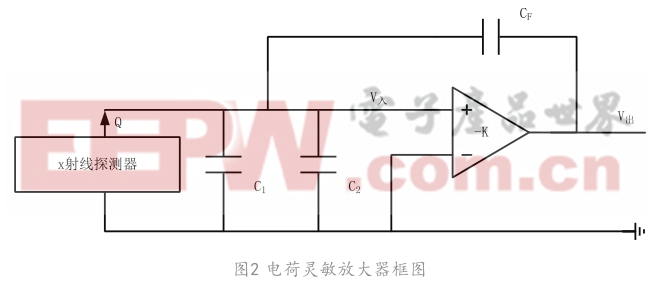

线阵X射线探测器在检测到X射线入射时,探测器输出一定数量的电荷Q,电荷Q的大小与入射X射线的强度成正比。若使用电压型放大器放大信号,则输入电压 V入 =Q/(C1+C2),其中C 1 为探测器输出信号到地间的电容;C 2 为放大器输入电容与分布电容的总和。半导体极间的分布电容C 2 受环境温度、外加偏压等因素变化,即在不采取有效措施的情况下,即使探测器输出的电荷Q是固定的,输入电压 V 入 也会随C 2 变化而变化,从而 V 入 与Q成非线性关系。因此,普通电压放大器在输出时,输出电压V 出 不稳定,不能得到V 出 与Q的线性关系。而电荷灵敏放大器,相当于一个开环增益很大的电容负反馈放大器, V 出 不受C 2 变化的影响且与探测器Q值成正比,电荷灵敏放大器如下图2所示。

放大器输入端电压V 入:

上式中,Q为探测器X射线照射后输出的电荷,K为放大倍数,C 1 为探测器对地的电容,C 2 为放大器输入电容及分布电容,C F 为反馈电容。

在满足上述条件时,V 出 与Q成正比,比例系数与反馈电容相关。在电荷灵敏放大器中,反馈电容不会改变为定值,于是放大器的输出电压反映了探测器的输出电荷大小。为了使探测器放大后的信号之间保持一致性与均匀性,使用DT64通道集成电荷灵敏放大器来对多通道的电荷信号进行放大。

对安检设备中线阵X射线探测电路ADC的要求,ADC需具有较高的分辨率,分辨率决定这图像数据的深度,为了保证图像数据的精度,通常使用16位以上分辨率的ADC;ADC应具有足够的采用率,满足在放大器信号输出时间内完成采样,本设计中电荷灵敏放大器对放大64路信号的输出时间分别为1 µs,因此对于ADC(模数转换器)的采样率应大于1 Mbit/s;综合尺寸、功耗、工作环境温度等多方面的因素考虑,选用TI公司设计的ADS8861模数转换器,其特点是16位,采样率为1 Mbit/s,全差分输入,串行输出的SAR模数转换器。

1.3 千兆以太网R G M II数据传输模块

X射线安检系统一般需要多块探测板进行级联,一块探测板具有128个探测点,针对大型的应用环境可能为上千个探测点,因此在实际工作工程中,对图像数据快速、准确的传输有很高的要求。理想情况下数据速率计算公式如下:

数据速率=[lines / s] × [板的数量] × [128像素/板]× [16比特/像素]= [x Mbps] (2)上式中[Lines/s]为积分器每秒放大的像素行,因为积分器工作周期为1 kHz,因此得到1 000 Lines/s。板的数量在普通车站、地铁、机场对行李箱安检的应用环境下最小为12块,针对海关的集装箱安检的应用环境所需板的数量最大为80块。因此在理想条件下得到最小的传输速率为24.576 MMbit/s,最大的传输速率为163.84MMbit/s。此速率仅为图像数据的传输,在实际数据传输中,为了保证数据的准确性还需考虑数据包的封装格式与相关的指令,因此大于理论的传输速率。另外对于X射线的安检设备,在系统与PC上位机的数据传输之间会有一定的距离,在大型的应用环境中需要采用较长的传输距离,为了保证数据传输的稳定性与精准度,本文采用千兆以太网进行对数据的传输,采用RTL8211D千兆网卡芯片。

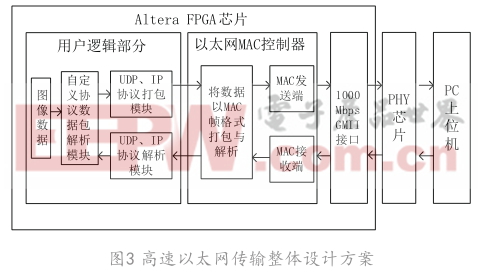

本文千兆以太网数据传输根据TCP/IP协议的网络通信架构设计,整个传输的结构包含用户层、传输层、网络层、数据链路层、物理层。千兆以太网数据传输的总体设计架构如图3所示。

用户逻辑部分设计部分包含用户层、传输层、网络层,主要负责根据用户自定义数据格式以及UDP、IP协议将数据进行特定格式打包与解析操作。以太网MAC控制器构成数据链路层,控制发送帧与接收帧的操作,并且负责对上层输的数据进行MAC帧打包,对从接口发送来的数据进行解析。PHY芯片组成物理层,通过FPGA的控制信号,完成对数据包的封装,并且时序控制PHY芯片将数据转化为波的形式传输给PC上位机 [5] 。

2 X射线探测系统的控制逻辑

2.1 图像采集时序控制

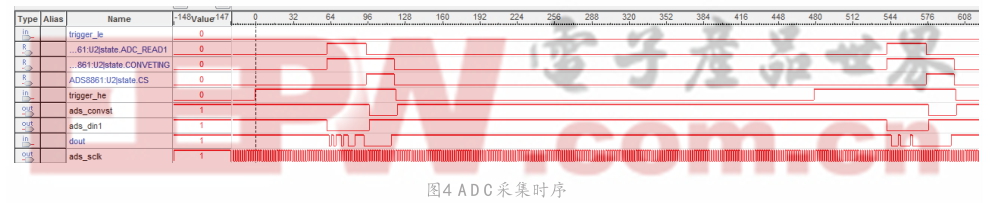

图像采集时序主要是FPGA对探测器的积分器与ADC采样时序控制如图4。每采集板都安装线阵X射线图像传感器,每块板在接收到X射线光照射时会均匀产生与光强相对应的电流信号。通过时序控制增益可控的多路积分器对电流信号进行放大,并让ADC在规定的周期内对放大的信号进行采集,此处使用一个16位ADC分别对高低能积分值进行采样。

2.2 千兆以太网数据传输

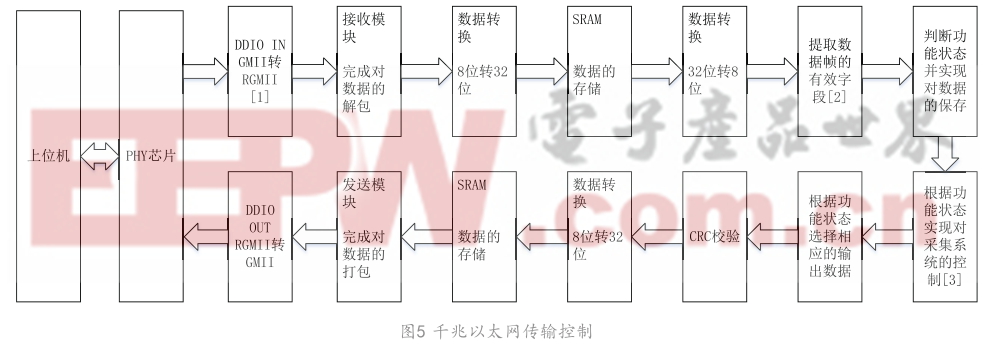

如图5所示,由PHY芯片发送的四位数据通过DDIO模块转化为8位数据供后续模块处理。接收模块对数据解析并存储,然后将数据的有效字段提取出包括CMD、OPE、DM ID、SIZE,通过判断有效字段可以知道要执行何种功能。数据板会发送给采集板相应的信号让采集板完成对应功能。之后再将得到的数据传输通过CRC校验并发送。

3 结论

本文提出一种以FPGA为控制核心,结合图像采集模块与千兆以太网传输模块的线阵X图像传感器采集传输系统。根据不同的应用场景,可选择不同块数的X射线探测器与采集板,采用菊花链数据传输结构方式以应对不同规模的场景。 千兆以太网的传输确保了图像数据的实时、高速与精准度,具有良好的应用价值与市场。

参考文献

[1] 郑金州,鲁绍栋.X射线技术在安检领域的应用[J].CT理论与应用研究,2012,21(02):357-364.

[2] 杨雷,高富强,李岭,等.高速低能X射线工业CT数据采集与传输[J].计算机应用,2014,34(11):3361-3364.

[3] 赵妮.基于X射线探测技术的电路设计[J].核电子学与探测技术,2011,31(07):779-782,81.

[4] 丁祥,胡晓君,张鲁殷,等.基于一种X射线平板探测器采集电路的设计[J].电子元器件与信息技术,2017(01):71-80.

[5] 张威.基于FPGA的高速以太网接口设计和实现[D].成都:电子科技大学,2016.

本文来源于科技期刊必威娱乐平台 2019年第9期第44页,欢迎您写论文时引用,并注明出处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码