100MHz 数字存储示波表样机的研究与试制----数据采集系统设计(二)

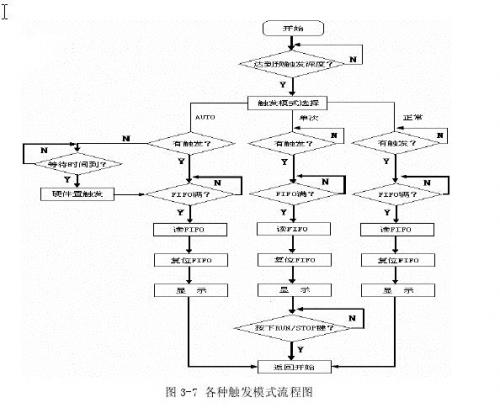

3.3.2触发模式选择

触发模式的选择实际上是当系统检测到或没检测到触发脉冲时,为了稳定的显示信号波形,对系统所作响应的选择。触发模式分为以下几种:

(1)自动模式:这是一种最常用的触发模式。当示波器在一定时间内(根据SEC/DIV设定来确定)未检测到触发信号时强制示波器触发。

(2)正常模式:示波器工作在这种模式下时,只有检测到触发信号时才产生有效的触发。

(3)单次模式:如果希望示波器在捕获单次波形后停止,可使用单次触发。它是通过示波器面板上RUN/STOP键来实现的。当示波器检测到触发信号后,捕获这次触发的波形,然后停止。直到用户再次按下RUN/STOP键,再捕获一次触发的波形。各种触发模式流程如图3-7所示。

触发状态读数:示波器在显示屏顶端中间位置处显示各种图标,以指示触发状态:

◆Armed(准备)表示示波器正在捕获预触发数据。准备期间,示波器将忽略触发。

◆Ready(就绪)表示示波器已捕获所有预触发数据,并且准备好检测触发。

◆Trig‘d(已触发)表示示波器已被触发,正在捕获后触发数据。

◆Stop(停止)表示示波器已经停止捕获数据。按下RUN/STOP按钮重新启动捕获。

◆Auto(自动)表示示波器处于自动触发模式,并且正在无触发的状态下捕获波形。

3.3.3预触发

在许多实际应用中,大量的情况是事件的发生不能预测,往往观察事件发生前的情况比观察事件本身更重要,而且许多单次现象的测量也要求显示触发点以前的信号,以便寻找该现象产生的原因。例如,当一个半导体器件导通时,其输出信号的幅度可能很大,我们可以用它来触发示波器。但是,如果我们要研究该半导体器件开始导通时很小的输入信号时,我们就会发现这个信号因太小而不能准确的触发示波器。这就要求示波器具有预触发功能,即将输入信号作为源信号接入通道1或者通道2,然后用器件输出信号作为外触发来触发示波器。通过示波器的预触发功能,我们就可以了解到该器件的输入信号在导通前后的变化情况,从而看出器件响应的因果关系。

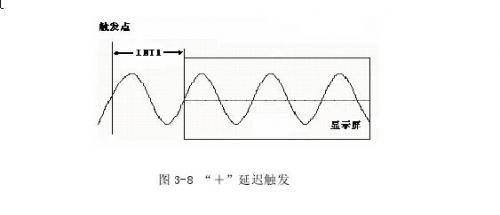

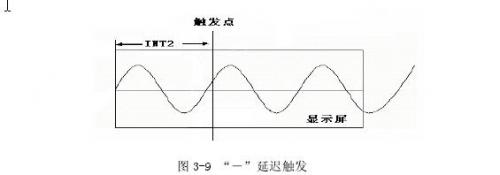

模拟示波器虽然有延迟线,但是,它也只能具有很小的视在延迟时间。数字存储示波器的预触发能力就很强。我们可以通过设置预触发深度的大小来方便的显示触发前后不同时刻的波形。通常,预触发是由延迟触发来实现的。延迟触发分为“+”延迟触发和“—”延迟触发。所谓“+”延迟触发,就是指触发前FIFO的写时钟等于读时钟。触发来后,“+”延迟计数器INT1开始计数。延迟计数过程中,FIFO的写时钟同样等于读时钟。也就是说,触发前直到INT1计数结束FIFO里没有波形数据。当达到计数值后,保持FIFO写时钟,关闭FIFO的读时钟,等到采样数据写满FIFO后将数据拿去处理。它的功能实现在实际过程中就好像整个显示屏幕的波形向左移。如图3-8.所谓“—”延迟触发,就是指存在一个“—”延迟计数器INT2,在触发前FIFO里已经存储了INT2计数值数量(即预触发深度)的波形数据,并在触发到来之前保持预触发深度不变。当触发来之后,写满整个FIFO再读出送去处理。它的功能实现在实际过程中就好像整个显示屏幕的波形向右移。如图3-9.

“—”延迟触发功能是基于FIFO能够存储触发前的信号,它的触发点只是FIFO内的一个参考点,而不是获取的第一个数据点,触发点前后的数据都被存储。当示波表对被测信号连续采样时,触发信号不是用来启动FIFO,而是用来确定什么时候冻结FIFO.因此,恰当的设计逻辑电路就可以把触发信号之前任意预先确定时间长度内的波形显示出来。但通常由于受到存储器大小的限制,预触发深度还是有一个极限值的。

3.4采样

采样分为实时采样和非实时采样。其中,非实时采样包括顺序采样和随机采样两种。本项目中,我们采用了实时采样和随机采样技术。以下我们将对这三种采样方式做详细的介绍。

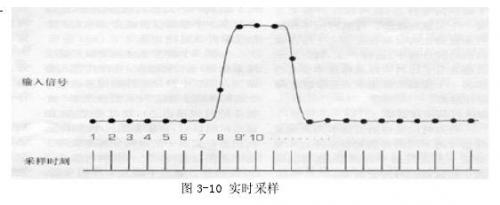

3.4.1实时采样

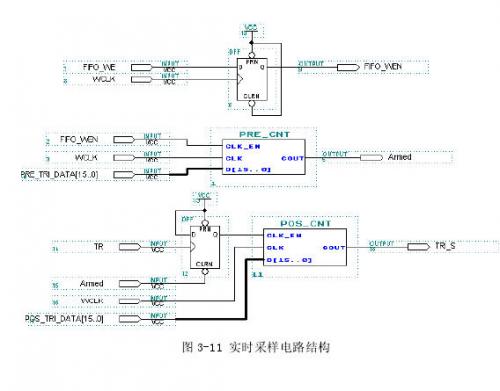

实时采样是一种最基本的采样方式。由奈奎斯特定理知,采样频率必须大于信号最高频率的两倍,才能不失真的恢复原信号。但实际上以接近奈奎斯特判定频率两倍的速率去采样的话是很难获得测量精度的,所以通常是以信号频率的5倍甚至10倍的频率去采样。实时采样的原理图如图3-10.实时采样是

在触发后的一个周期内,连续高速的对信号进行采样,一次捕捉完这个周期内信号的全部波形数据。它的特点是:1.采样频率高于信号频率;2.能够捕捉单次信号和缓慢信号。这时,示波器的带宽称为单次带宽或实时带宽,它主要取决于最大数字化采样速率(即A/D的最大转换速率)和所采用的显示恢复技术。

1.实时采样的实现

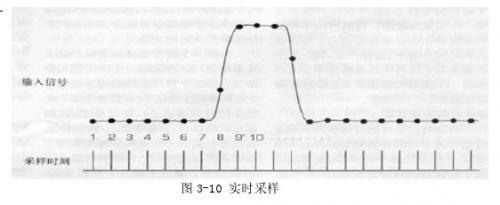

实时采样电路的主要结构如图3-11.

首先,在每个写时钟(WCLK)检查DSP是否发出FIFO写使能信号(FIFO_WE)。当检测到写使能信号,FIFO写使能(FIFO_WEN)有效,前置计数器PRE_CNT(相当于3.3.3节的INT2计数器)根据预先设置好的预触发深度,按照写时钟计数。此时,FIFO只有写时钟有效。当预触发满后,允许触发信号(TR)。在等待触发的过程中,FIFO读时钟等于FIFO写时钟。当触发信号到来,则使能后置计数器POS_CNT(相当于3.3.3节的INT1计数器)根据预先设置好的延迟触发时

间,同样按照写时钟计数。当计数结束后发出TRI_S信号关闭FIFO读时钟,使FIFO只写不读直到FIFO写满,完成一次数据采集。注意,前置计数器PRE_CNT和后置计数器POS_CNT里的计数值分别代表触发点位于屏幕内外时距屏幕最左端的距离,所以,这两个计数器不会出现同时置数的情况。

2.实时采样的显示

当FIFO里数据采集满以后,就要将数据读回显示。由于本系统设计的存储深度为2.5K,而显示屏时间轴上的点数为250,所以显示时要将采集的数据抽点显示,即将每10个点当中的两个点显示在同一个时间轴上,其中一个为最大点,一个为最小点。波形显示有点显示和连线显示两种方式。点显示方式下,将2.5K FIFO的数据读回以后,每隔10个点中取出最大值和最小值,然后显示在同一时间轴上。当在连线方式下时,则要将前一个时间轴上的最大最小值和后一个时间轴上的最大最小值相比较,根据比较结果将点连线显示。

由于AD采集的数据是8位,即取值范围在0~255之间,而LCD上的幅度轴上只有200个点。这样必须要将采集的数据作相应的处理。即若数据小于28的,在显示屏上作0处理,大于228的作200处理,其他的数据都减去28后作显示的数据。这样保证了所有的采集的数据都在波形显示区了。

3.4.2顺序采样

顺序采样是一种等效时间采样,它不是在一个信号周期内捕获全部的采样点,而是每个信号周期只捕获一个采样点。当第一个触发事件到来以后就立即采集第一个采样点,存入存储器。第二个触发事件到来后,由一个定时器产生一个很小的时间延迟△t,经过这个△t的延迟时间以后再采集第二个采样点。第三个触发事件到来后,该定时系统则产生2△t的延迟时间。此延迟时间过后再采集第三个采样点,并这样进行下去。这就是说第n个新的采样点的采集是在相对于相同触发事件延迟了(n-1)△t的时间以后进行的。其结果是示波器上显示的波形是由按固定次序出现的采样点构成的。即第一个采样点在屏幕的最左边,接着各采样点依次向右构成显示波形(如图3-12)。在顺序采样模式下,采集波形的周期数,即触发事件数等于所捕获采样点的个数。顺序采样可以实现“+”延迟触发,但由于它的采样都发生在触发事件后,所以顺序采样不能提供预触发信息。本项目中没有采用顺序采样技术,所以在这里只对顺序采样做概念性的介绍。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码