锂离子电池管理芯片的 研究及其低功耗设计 — 锂离子电池管理芯片的电路实现

4.1混合信号电路的设计流程

图4.1.1是混合信号VLSI的top-down详细设计流程。对于前端(Front-end)设计,有全定制、半定制和基于标准单元这三种主要设计方法。基于标准单元的设计方法中,需要先对模块进行完整清晰的定义,然后进行RTL编码和可测性设计,再对整个芯片设计进行验证。采用逻辑综合器,将RTL描述转换成门级描述,而门级描述与所选工艺的标准单元库密切相关。为了跳过这个综合设计阶段,可以从电路结构设计开始,采用SPICE模拟以确定延迟和功耗在预算之内,然后产生一个门级网表来完成后处理任务(如插入扫描测试缓冲器来调整时钟偏差等),再接下来的整个设计流程和综合设计中的类似。

需要指出的是,在IC行为级模型阶段,模拟电路单元需要考虑四种因素:行为、电路结构、模型和功能。考虑功能的目的在于检查包括模拟单元在内的系统的连接性,行为考虑则对功能设计验证有帮助,事实上,行为因素仅仅需要在分析瞬态模型中,它只对稍大电路模块的验证有效,所以并不需要DC或AC模型。在上述因素中,SPICE级的电路结构代表了电路真实性能,而行为描述只给出了单元的功能特点。

从整个晶体管级描述到最后版图生成,是后端设计(Back-end)所包涵的内容,即后端综合和布线优化。这个设计阶段也被称为物理设计阶段,广义地这个阶段包括物理设计、模拟和验证。在混合信号设计中,可以分为两个设计流程:数字设计流程和模拟设计流程。

模拟设计流程需要版图设计、设计规则检查、电学规则检查和LVS比较。

通过LVS检查后,还要进行后版图验证,此时版图提取将考虑寄生效应所产生的寄生电阻、电容和电感等参数影响。后版图模拟对时序、功耗的验证很重要,对整个芯片验证也是不可缺的一步。

可以将后端设计中的数字部分视为模拟版图设计的一个附加步骤。在经过版图设计后,和模拟部分一起进行整个芯片的Back-end验证。Back-end设计的最后一个阶段中,便是在版图中加入I/O pad,保护环等。

图4.1.1中还给出了在设计各阶段所需要用到的设计软件。本章所涉及的是电路的设计部分,而功能、性能验证和版图设计都将在下一章讨论。

4.2控制电路设计

4.2.1控制电路

控制模块中,关键是是状态转换信号的生成,这其中有表示工作状态的逻辑信号输出,还有控制内部模块的功耗控制信号。显然,前者是由系统有限状态机所决定,而后者是由第三章所提出的功耗管理状态机所决定。下面,就这两方面分别加以阐述。

1有限状态机模型

系统有限状态机(FSM)如图4.2.1所示。

从图中可以看出,在相应条件下,系统能输出设计所要求的状态信号,控制CO及DO输出端信号。影响状态改变的参数如下:一是电压检测信号,有过充电电压检测信号V CU、过充电电压释放信号V CL、过放电电压检测信号VDU和过放电电压释放信号VDL;二是VM端过流检测信号,包括过流1检测电压VIOV1、过流2检测电压VIOV2、负载短路检测电压VSHORT和非正常充电检测电压VCHA;三则是延时时间参数,有过充检测延迟时间tCU、过放延时tDL、过流1延时tIOV1、过流2延时tIOV2等。

在如图4.2.1所示的各个状态下,输出端CO、DO信号为:

①正常状态:DO=CO=1

②过充状态:DO=1;CO=0

③过放状态:DO=0;CO=1;VM→V DD

④放电过流状态:DO=0;CO=1;VM→V SS

⑤非正常充电电流状态:DO=1;CO=0;

⑥零伏电池充电抑制:DO=0;CO=0;

⑦Power Down状态:DO=0;CO=1;I DD =I PDN

2控制逻辑设计

控制逻辑(Control Logic)电路是芯片的关键部分之一,电路的延时和相应的逻辑控制都在这部分实现,功耗管理的控制逻辑也包含在这个模块中。

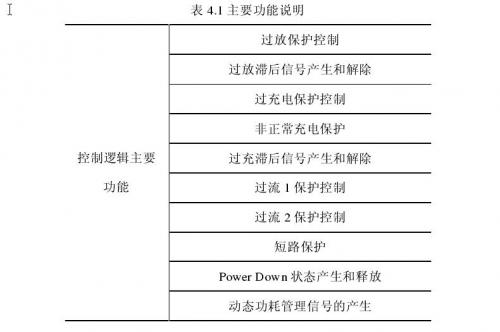

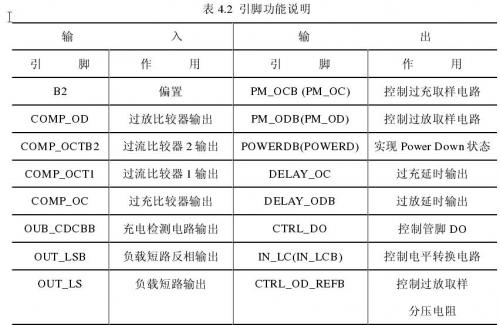

1)模块I/O端口说明图4.2.2给出了逻辑控制模块的框图,表4.1和表4.2给出了模块的功能说明以及各端口的定义。

2)延时信号设计

从前面系统功能分析可知,芯片的控制精度不仅取决于检测电压精度,还和延时控制密切相关。保护功能实现过程中,需要过充、过流2、过流1和过放这四种不同的延时控制,四种延时信号的选择原理如图4.2.3所示。

图4.2.3中,当计数器触发工作后,输出周期不同的连续方波信号。方波前半个周期为延时时间,延时结束后计数器输出端由“0”跳变为“1”,该跳变信号为有效的延时控制信号。计数器延时输出到图中的保持电路Hold后,通过Hold电路将跳变信号锁定,从而可以使电路经过延时后,达到控制DO或CO端翻转的目的。图中,分别与Hold相接的NOR5~NOR8可看作具有置位端B的反相器,其作用是选择有用信号将其从A端传到Y端,而屏蔽无关信号,防止误动作。

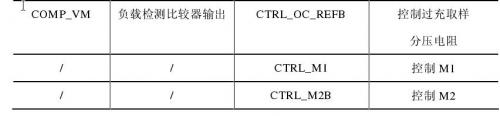

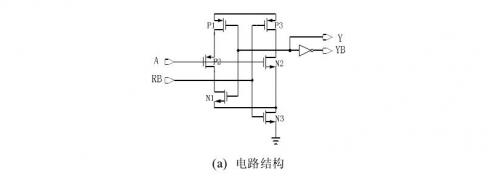

在整个电路中,Hold起锁定延时控制信号的作用。图4.2.4为Hold电路的内部原理图和电路符号表示。

图4.2.4中,电路输入端为A,RB,输出端为Y、YB.电路输入和输出的逻辑关系如下:当RB=0时,Y=0、YB=1,Y、YB与A无关;当RB=1时,只要输入端A为高电平,Y即可输出稳定的高电平,YB输出稳定的低电平。即信号锁定后,Y、YB与信号A无关。

3)保护功能实现

①过放电保护控制

过放电保护控制逻辑电路如图4.2.5所示。

当系统由正常状态转化为过放电状态时,过放电比较器的输出COMP_OD由高电平转化为低电平,此时NOR6的输出Y能跟随输入端A的变化而变化。

COMP_OD还通过NAND8使NOR10的输出端Y由“1”跳变为“0”,因为Y与COUNTER的R端直接相连,因此R也变为“0”,启动COUNTER;此时INV7输出端由“0”跳变为“1”,启动H6,在H6和计数器共同作用下,H2~H5开始工作。当过放延时完成后,H3将QB9的上升沿反相锁定并输出到NOR6的A端,NOR6的输出Y经NOR3、NAND1使NOR4的Y端(也即CTRL_DO端)由“1”

跳变为“0”;再通过后续的两级反相使DO由“1”跳变为“0”,从而起过放保护作用。

当COMP_OD由“1”转化为“0”时,它还通过INV9使NOR13的输入端B变为“1”,这样就确保NOR13的输出不会在过放电时变为“1”,M2也就不会导通,就不会使放电回路切断。

②过放电滞后信号产生和解除

一旦过放电延时时间结束,过放电保护就开始起作用,CTRL_M1由“1”变为“0”。此时,如果非正常充电电流检测电路的输出OUT_CDCB为“0”,CTRL_OD_REFB由“0”变为“1”,即产生过放电滞后信号,电路由图4.2.6给出。

当过放电状态结束时,CTRL_M1变为“1”,CTRL_OD_REFB变为“0”,过放电滞后解除;当充电器检测电路的输出由OUT_CDCB为“1”,即使在过放电保护起作用时,CTRL_OD_REFB也为“0”,过放电滞后解除。

③过充电保护控制

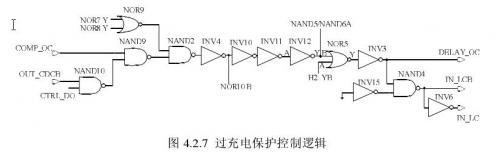

当系统发生过充电时,过充电比较器的输出COMP_OC由“1”跳变为“0”,它通过NAND9、NAND2使INV4的输出端Y由“1”跳变到“0”,控制逻辑如图4.2.7所示。

I一方面,NV4的输出信号通过INV10、INV11、INV12反相使NOR5的B端由“1”变为“0”,此时NOR5的Y端能随A端的变化;同时,INV12的输出也输入到NAND5、NAND6的B端,使系统在过充电状态下,禁止过流1和过流2保护起作用。

另一方面,NV4的输出信号输入NOR10,使NOR10输出端由“1”变为“0”,和过放电类似,启动H6、COUNTER开始工作。当过充延时完成的时候,H2将QB12的上升沿反相锁定后输出给NOR5,NOR5的Y端由“0”跳变为“1”,通过INV3、NAND4使过充延时信号DELAY_OC由“1”变为“0”、IN_LCB由“1”变为“0”,再通过INV6使IN_LC由“0”变为“1”,IN_LC、IN_LCB信号送电平移位电路处理后控制CO引脚输出合适的低电平,从而实现过充电保护。

④非正常充电电流保护

当充电电流过大,充电检测电路通过VM端检测到后,输出OUT_CDCB由“0”变为“1”,NAND10的输出端由“1”变为“0”,NAND9的输出由“0”变为“1”,此后就和过充电保护过程一样,最终控制CO输出合适的低电平,以切断充电回路,起保护作用,控制电路见图4.2.7.在过放电保护起作用时,需要禁止非正常充电电流保护,所以还将CTRL_DO的信号送入NAND10的A端。这样,在CTRL_DO由“1”变为“0”时,使NAND10的Y端信号不受充电器检测电路输出OUT_CDCB的影响。

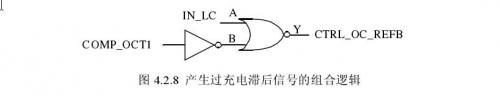

⑤过充电滞后信号的产生和解除

一旦过充电延时时间完成,过充电保护便开始起作用,IN_LC由“1”变为“0”。此时,如果过流1比较器的输出COMP_OCT1为“1”,CTRL_OC_REFB则由“0”变为“1”,这就是过充电滞后信号;当过充电状态结束时,IN_LC变为“1”,CTRL_OC_REFB变为“0”,过充电滞后解除。图4.2.8是过充电滞后信号的组合逻辑电路图。

另外,当过流1比较器的输出COMP_OCT1为“0”时,即使在过充电保护起作用时,CTRL_OC_REFB也为“0”,过充电滞后解除。

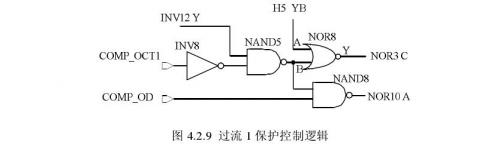

⑥过流1保护控制

当过流1比较器的输出端COMP_OCT1由“1”变为“0”时,如图4.2.9所示,信号通过INV8、NAND5后,将NOR8的B端置为“0”,此时NOR8的Y端将跟随A端变化;同时,NAND5的输出将NAND8输出置为“1”,和前面分析类似,通过NOR10启动计数器。当过流1的延时完成时,H5的延时信号送入NOR8的A端,NOR8输出端由“0”变为“1”,再通过NOR3、NAND1、NOR4使CTRL_DO由“1”变为“0”,从而控制DO由“1”跳变为“0”,起过流1保护作用。

另外由图4.2.5可知,只要系统不是过放电状态,NOR13的B端始终为“0”,而出现过流1时的A(CTRL_DO)端将由“1”变为“0”,所以Y端(CTRL_M2B)将由“0”变为“1”,控制M2导通,使过放电流从M2流走。

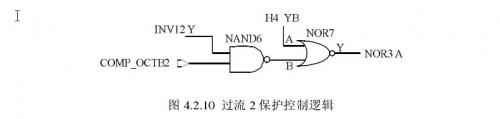

⑦过流2保护控制

当过流2比较器的输出COMP_OCTB2由“0”变为“1”时,如图4.2.10所示,通过NAND6,使NOR7的B端由“1”变为“0”,NOR7的输出Y与输入A成为反相关系。由于过流2的发生之前一定已经有了过流1,因而计数器已经启动,延时的计时从过流1算起。

如果过流1发生后在2ms之内进入过流2,则过流2延时2ms;因为过流1延时为8ms,如果过流1发生后在2ms之后8ms之前进入过流2,则过流2延时2ms与8ms之间。当过流2延时完成,NOR7的Y端由“0”变为“1”,同样通过NOR3、NAND1、NOR4使CTRL_DO从“1”变为“0”,控制DO由“1”跳变为“0”,起过流2保护作用。

4)功耗管理信号设计

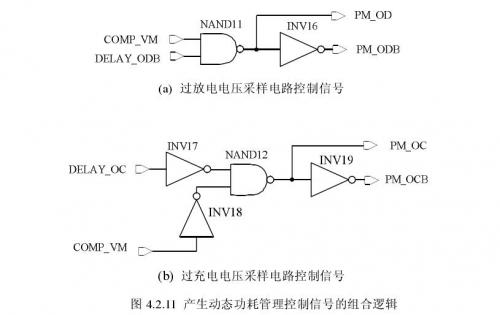

①动态功耗管理控制

图4.2.11(a)和(b)给出了产生动态功耗管理控制信号的组合逻辑图,其中,图(a)输出信号PM_ODB用来控制过放电压取样电路,而(b)中输出信号PM_OCB用来控制过放电压取样电路。

图4.2.11(a)的电路工作原理如下:COMP_VM是负载检测比较器输出信号,其值为“1”时代表所接负载为充电器,此时NAND11输出信号完全由过放延时输出DELAY_ODB决定。正常工作时,DELAY_ODB为“0”,则经过两次反相后,PM_ODB输出也为“0”,控制过放电压取样电路能正常工作;当出现了过放,在延时结束后,DELAY_ODB由“0”跳变为“1”,则对应PM_ODB也输出“1”,关断过放电电压取样电路。而在COMP_VM输出“0”时,代表所接负载为放电负载,此时DELAY_ODB不再起作用,PM_ODB始终为“0”,保证能进行过放电电压取样。

图4.2.11(b)中,当所接负载为充电器时,COMP_VM输出为“1”,经INV18反相后输入NAND12,则此时NAND12的输出与过充延时信号DELAY_OC无关,始终为“1”,则反相后PM_OCB始终为“0”,过充电电压采样不受影响。

但是在接上负载放电时,COMP_VM跳变为“0”,此时NAND12输出信号完全由过充延时输出DELAY_OC决定。和前面分析相似,在放电情况下,正常工作时,DELAY_OC输出为“1”,经三级反相后PM_OCB输出为“0”,过充电电压采样电路能正常工作;而当过充电产生并且延时结束后,DELAY_OC跳变为“0”,反相后PM_OCB输出为“1”切断采样通路。

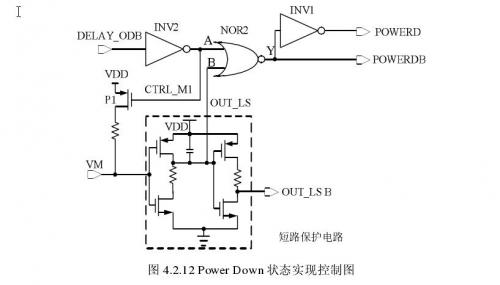

②Power Down状态控制Power Down状态实现图见图4.2.12.当过放延时结束后,过放延时信号DELAY_ODB由“0”跳变到“1”,经INV2反相后CTRL_M1由“1”跳变为“0”,此时NOR2输出状态(POWERDB)由输入端B(OUT_LS)来决定。CTRL_M1为低电平时,P1导通,将VM端电位升高,一旦VM电压值升到比V DD低1.3V时,OUT_LS将变为低电平,因此POWERDB由“0”跳变到“1”,POWERD由“1”跳变为“0”,从而使振荡器、所有的比较器停止工作,系统进入低功耗状态,也就是Power Down状态。

从上述过程可知,Power Down状态的实现有赖于VM电位的升高。虽然仅从进入Power Down状态的角度来看,完全可以把DELAY_ODB端作为POWERDB直接输出,但是此处强调进入Power Down状态还要受VM控制,一个重要的原因是为了实现Power Down状态的退出。因为一旦电路进入PowerDown状态以后,过放比较器已停止工作,DELAY_ODB信号将保持不变。为了退出Power Down状态,需对电池进行充电,充电后VM电位下降,OUT_LS电位升高,POWERDB可以由“1”跳变为“0”,于是就实现了Power Down状态的释放。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码