详解JESD204B串行接口时钟需求及其实现方法

2.JESD204B时钟的实现

2.1专用的JESD204B时钟芯片

LMK04820系列的时钟芯片是一款专用的JESD204B时钟芯片,Device Clock和SYSREF是成对输出的,其输出的时序满足其时序要求,应用较为简单,但当用户需要连续模式的SYSREF时,会引起一定串扰如下图所示(983.04MDevclk and 7.68MSysREF),可能会造成数模转换器的性能下降。当然SYSREF工作在脉冲模式,LMK04820是一个完美选择。如果板上JESD204B时钟路数较多,LMK04820的输出不能满足要求,可以用LMK1802扩展得到更多的时钟输出。

图3

2.2通用的LVDS时钟芯片

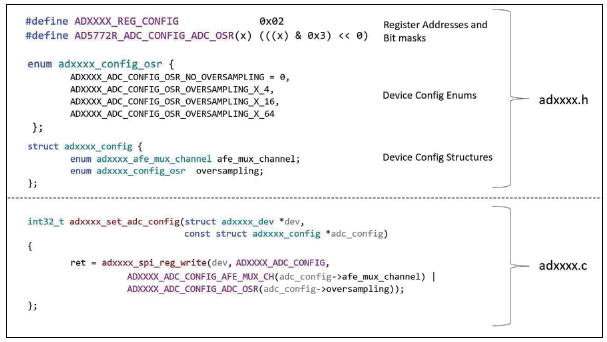

在某些应用中客户的系统上既有JESD204B的数模转换器,也有LVDS接口的数模转换器,或者客户需要用到连续模式的SYSREF,这时LMK04800系列的时钟芯片是理想选择。LMK04800是带有输出延时调整的去抖芯片,我们调整其输出的延时,使得两路不同通道的输出的时序满足JESD204B时序的要求,分别作为Device Clock和SYSREF.因此延时调整是LVDS时钟芯片实现JESD204B时钟的核心。

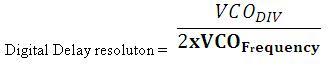

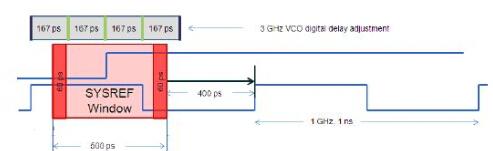

LMK04800的输出有数字延时和模拟延时,在多数应用时数字延时的调整精度已经能满足了,因此不推荐模拟延时调整,另外模拟延时会带来输出时钟噪底的恶化,一般会恶化3-5db.数字延时的精度取决于第二级集成VCO

如果VCO_DIV没有用或者用外部的VCO,则分子必须等于1.当延时设置完成后,必须有同步事件才能使得设置生效,同步可以通过寄存器,硬件管脚去触发。当明白了数字延时的调整精度,再结合PCB传输延时就可以计算出最大的调整误差。如果Device Clock是1GHz,而此时VCO的频率是3GHz,则根据上面公式调整精度是167ps,另外我们需要考虑到器件不同输出通道的Skew,这里假设±30ps,另外还需要考虑到SYSREF和Device Clock的PCB长度不等长,这里假设0.5cm,约±30ps,则我们可以得到SYSREF可调整的窗口:

图4

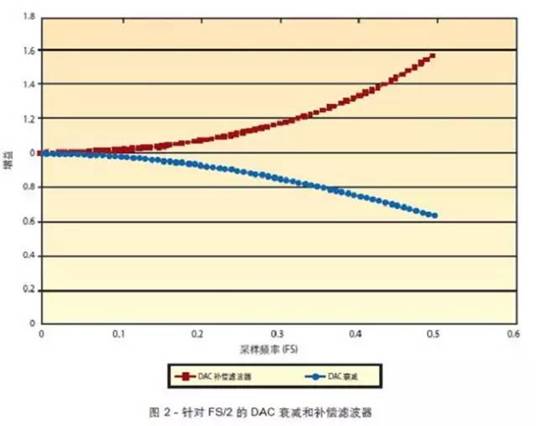

图中400ps是LMK04800 LVDS的输出的上升沿和下降沿所用时间(上升沿和下降沿都是200ps)。图中我们可以根据以上的条件计算得到调整精度是167ps,Device Clock的周期是1000ps,则可调整的窗口为1000-400-120=480ps,即为红色的的影映区域,当SYSREF的上升沿在红色的区域调整时,Device clock可以容易的检测到SYSREF的上升沿,否则需要等到下一个Device clock周期才能检测到SYSREF上升沿。

3结论及其测试验证

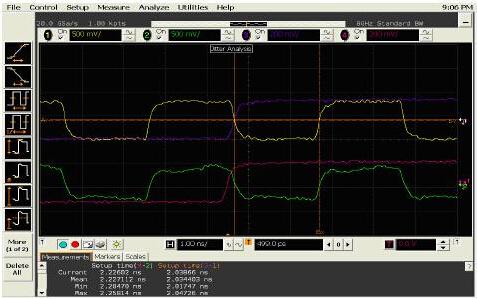

相比LMK04828($12.6000),我们用LMK04800和LMK01010($7.7512)产生JESD204B的时钟,既能满足

图5

全是JESD204B的器件的要求,也能很好的用在有LVDS接口需要的系统中。另外LMK04800是一款非常成熟的具有高延时精度的时钟芯片,其性能被用户广泛接受,同时在某些需要用延时调整去适应DPD算法的应用中也能很好提供完美时钟解决方案。如下图所示,这是通过调整LMK04800的输出延时,用示波器采集的JESD204B的时钟,其时序能很好的满足其标准。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码