PolarFireR FPGA Splash套件的JESD204B串行接口标准

Microchip的PolarFireR FPGA产品业界认证具有出色可靠的低功率、高安全性组件,一直被广泛应用于有线和无线通信、国防、航空、工业嵌入式、人工智能、图像处理等不同范畴。本文将介绍如何在PolarFire Splash套件上实现JESD204B独立设计,并搭配GUI演示应用的电路板。此设计是使用PolarFire高速构建的参考设计收发器模块,以及CoreJESD204BTX和CoreJESD204BRX IP内核。它在运行时透过收发器将CoreJESD204BTX数据发送到CoreJESD204BRX IP内核。此设置有助于独立的JESD不需要模拟转换器(ADC)或数字转换器接口。

Microchip的PolarFire FPGA具有嵌入式高速收发器模块,可以处理的数据速率从250 Mbps到12.5 Gbps不等。收发器(PF_XCVR)模块集成了几个功能以支持 FPGA多种高速串行协议。JESD204B是一种高速串行JEDEC委员会制定的数据转换器接口标准。JESD204B标准减少了高速数据转换器和接收器之间的数据输入和输出数量。Microchip提供发射器的CoreJESD204BTX和CoreJESD204BRX IP 内核以及JESD204B标准的接收器接口。这些IP内核易于与JESD204B的数据转换器整合,以开发无线基础设施等高带宽应用收发器、无线电、医学成像系统以及雷达和安全通信。这些IP内核支持从x1到x8的链路宽度,以及每通道250 Mbps到12.5 Gbps的链路速率使用子类0、1和2。

设计要求如下表一列出了软件、硬件与IP运行展示所需的资源,大家也可从Microchip网站下载参考设计与开发软件来实现。

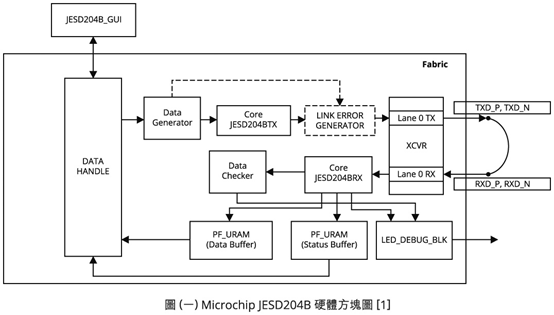

以下PolarFire JESD204B演示设计,连接符合JESD204B标准的数据转换器,它带有PolarFire的组件。这个设计中的硬件实现如图一所示。

1. DATA_HANDLE_0与GUI接口,GUI支持选择PRBS或波形输入。

2. DATA_HANDLE_0将输入选择传递给DATA_GENERATOR_0模块,后者生成相应的输入数据并将其发送到CoreJESD204BTX IP内核。

3. CoreJESD204BTX IP内核执行基于配置生成的JESD204B发送器功能,并将数据发送到PF_XCVR(收发器)IP内核。

4. 编码数据由CoreJESD204BRX IP内核接收,因为PF_XCVR模块的TX和RX通道被环回。

5. CoreJESD204BRX IP核根据配置执行JESD204B接收器功能,并将数据发送到 GUI以查看所选输入。

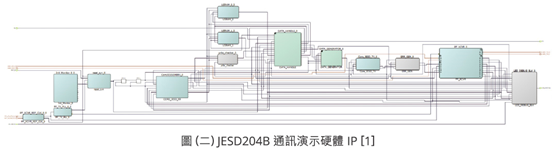

图二所示为在LiberoR SoC实现JESD204B通讯演示硬件IP。

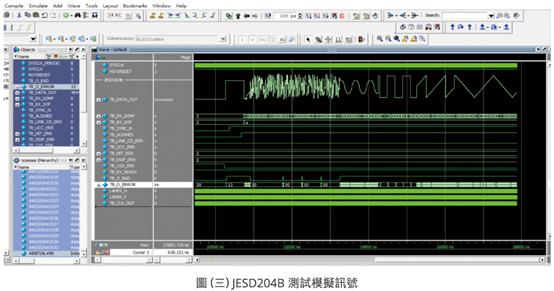

图(三)为透过Libero SoC 撰写测试模拟JESD204B所得的讯号。

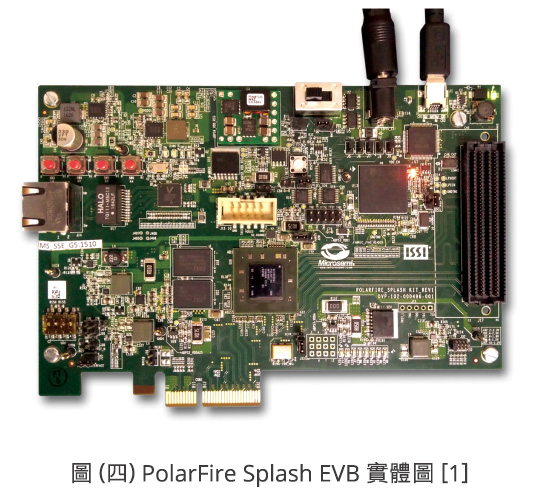

本文利用仿真验证,并确认此讯号无误,再将此开发设计程序烧入FPGA中做验证。图(四)开发实体参考设计PolarFire Splash EVB实体图。

利用PolarFire Splash EVB连接PC,并搭配GUI做验证,得到CoreJESD204BRX 收到的波形,如图(五)所示。由此图可得知实际测试与模拟的波形是相同。

本文所探讨JESD204B Standalone Interface,利用理论实作搭配GUI验证与仿真讯号分析,得到符合的讯号波形。以减少设计开发时程。若有任何疑问,欢迎参阅Microchip网页了解更多相关的产品信息,或与我们联络。

以下亦列出了更多有关JESD204B标准和IP内核的信息的供各位读者参考。

‧有关PolarFire收发器模块、PF_TX_PLL和PF_XCVR_REF_CLK的信息,请参阅UG0677:PolarFire FPGA收发器用户指南。

‧ 有关 PF_URAM(PF Micro SRAM)的更多信息,请参阅UG0680:PolarFire FPGA Fabric用户指南。

‧ 有关CoreJESD204BTX的更多信息,请参阅CoreJESD204BTX手册。

‧ 有关CoreJESD204BRX的更多信息,请参阅CoreJESD204BRX手册。

‧ 有关Libero、ModelSim和Synplify的更多信息,请参阅Microchip Libero SoC PolarFire网页。

参考来源:

[1] DG0796 Demo Guide PolarFire FPGA Splash Kit JESD204B Standalone Interface

本文作者为:Microchip主任应用工程师 郑世仁

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码