超宽带(UWB)定位系统发射机基带的系统设计,功能模块分解、硬件实现

3.1.1发射机主控单元

主控单元MCU 是整个发射机的核心模块,它控制所有子模块的工作,以保证整个发射机的时序正确,同时还承担者与MAC层交互通信的任务。由于每次发射处理都是MAC层发起的,因此MCU与MAC层之间采用中断的通信模式。为了能够精确的控制各个功能模块的处理时间,主控单元MCU采用计数的模式来进行控制。

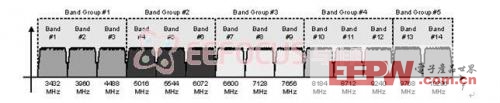

可以用状态图来描述MCU的工作过程,当MCU接收到MAC层发送来的请求信号(TXSTART_REQ)后,首先发送复位信号PHY_RST对整个处理器进行初始化。与请求信号同步串行输入的还有28位PHY_TXSTART信号,其中包括待发射帧长(LENGTH,12bit)、发射速率(RATE,5bit)、发射功率(TXPWR,3bit)、扰码器字段(SCRAMBLER,2bit)、突发模式字段(BM,1bit)、前导符类型字段(PT,1bit)、发射机TF码字段(TX_TFC,3bit)和发射机使用带组的最小有效比特(LSB,1bit)等发射参数,MCU接收完毕后将其送至相应的输出端口对处理模块进行控制。紧接着接收80bit的MAC头,按8位并行方式传输。并由RATE信号翻译出数据的编码方式,传输速率和每符号数据比特等等。

PSDU数据帧的输入是通过MCU向MAC层发送DATA_REQ请求来进行的,每发送一起数据请求,MAC层将送出一个符号的数据,数据的长度由发射速率(RATE)决定,并且根据LENGTH参数计算DATA_REQ的发射次数,即将LENGTH参数置入一计数器作为初始值,由于该参数表示的是数据帧的字节长度,因此每发送一次DATA_REQ后,LENGTH都要减去一个符号的字节长度,即生成一个符号的字节数,当计数器的值小于或等于0时,则发送结束。

的伪随机序列是由n阶线性移位寄存器产生的,但是线性移位寄存器所产生的序列并不一定是伪随机序列,他与联接多项式有密切关系。只有找到了本原多项式,才能由它构成伪随机序列的产生器。但是寻找本原多项式并不是很简单的。所以前人大量的计算已将常用本原多项式列成表备查,本系统使用一个长度为32767的帧同步扰码器加扰,帧同步扰码器使用的生成多项式为:

(3-1)

(3-1)

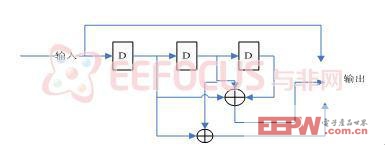

线性反馈移位寄存器的反馈逻辑输出输入数据进行模2相加,即可得到图3.5所示的扰码器的一般形式:

图3.5 扰码器原理图

3.1.3信道编码

根据系统传输信道的情况,为了保证通信系统传输的可靠性,克服信道中的噪声和干扰,专门设计了一类抗干扰的技术,这家就是各种信道编码。它根据一定的规律在待发送的信息码元中人为的加入一些必要的校验码元,在接收端利用这些校验码元与信息码元之间的监督规律,发现和纠正差错,以提高信息码元传输的可靠性。其中待发射的码元为信息码元,人为加入的多余的码元为校验码元。信道编码的目的是试图以最少的校验码元为代价,换取最大程度的可靠性的提高。这些方法虽然增加了信息的冗余度,降低了系统容量,但增加了发送符号之间的相关性,能够提高信息传输可靠性。

常用的信道编码有线性分组码、循环码、BCH码、RS码和卷积码等。本系统使用的编码为卷积码,卷积码是一种应用广泛的纠错编,下面对其原理详细的阐述。

卷积码也是分组的,与分组码的不同在于,卷积码的编码设计中存在记忆性。他的校验码元不仅与当前组的信息元有关,而且与此前若干组的信息元有关。这种码的纠错能力强,不仅可以纠正随机误差,而且可以纠正突发误差。输出与先前输入比特的相关性决定了卷积码的编码器是一个有限状态机。

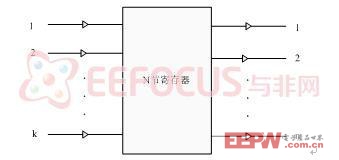

卷积编码器是用移位寄存器、加法器及乘法器用串联和并联的方式构成的特定的电路。一般可记为(n,k,N-1)码[27],其中N表示编码器中寄存器的节数,k表示每节寄存器的位数,n表示编码器输出码元位数,其约束长度为N位。每个时刻编码器输出n位码元,这不仅与当前的输入的k位码元有关,而且还与编码器中N级寄存器中信息码元有关。

卷积码编码器可看做由一个有k个输入端,n个输出端,且具有N节寄存器构成的一个有限状态,或有记忆系统,典型结构图3.6所示。

图3.6 卷积编码结构图

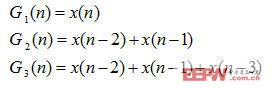

以(3,1,3)卷积码为例,如图3.7所示为一个约束长度为4,编码效率为1/3的卷积编码器。

图3.7 (3,1,3)卷积码编码器

(3,1,3)码的三个子生成元为:

(3-2)

(3-2)

所以,该码的生成多项式矩阵为:

(3-3)

(3-3)

该卷积编码器由3个移位寄存器D和2个模2加法器组成。每输入一个信息元就会编出两个校验码元 、

、 ,顺序输出成

,顺序输出成 、

、 、

、 ,码长为3,其中信息位仅占一位,由上式可知校验码元

,码长为3,其中信息位仅占一位,由上式可知校验码元 、

、 不仅与本组信息有关,还与前3组信息元有关。

不仅与本组信息有关,还与前3组信息元有关。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码