一种新型高速CMOS全差分运算放大器设计

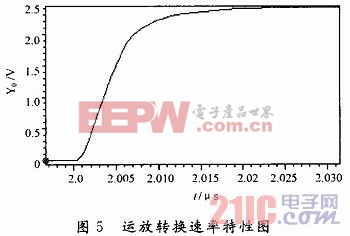

在运放输入端加入阶跃响应激励,在2μs时刻输入2.5 V的阶跃信号,仿真结果如图5所示,测得运放转换速率可达368.7 V/μs,建立时问为12.4 ns。

5 结语

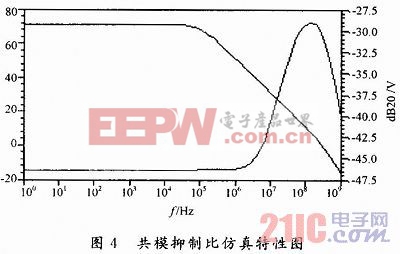

基于流水线ADC系统应用的要求,设计了一种新型的高速运算放大器。该运放采用全差分折叠式共源共栅结构为主运放和共源放大器差分输入对管对共模电平取样的连续时间共模反馈电路。同时使用了一种新的连接方法,在保证高速的同时提高了运放的稳定性。经仿真测得在2.5 V单电源并接0.5 pF负载电容的条件下,运放直流增益可达71.1 dB,单位增益带宽303 MHz,相位欲度52°,共模抑制比达117.4 dB,转换速率高达368.7 V/μs,建立时间12.4 ns。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码