DDR测试--SDRAM时钟分析案例

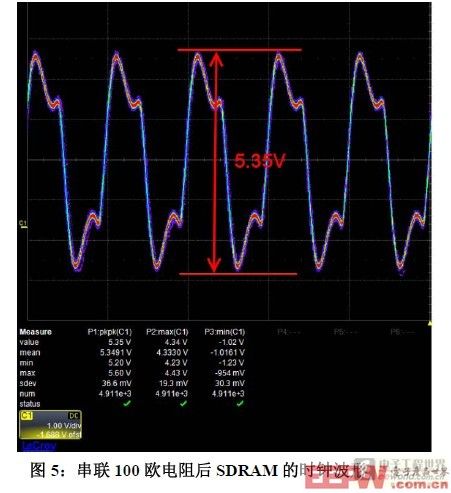

下图5所示为只串联100欧电阻时测量到的波形,信号有过冲,峰峰值为5.35V,偏大,对比图4的端接方法,串联电阻加上并联电容是较好的解决方法。

总结:在这个案例中,我们得到的以下经验:

1、串联匹配是较好的SDRAM的时钟端接策略,在原理图设计中,需要加上串联的电阻和并联的电容,如果MCU输出的时钟驱动能力弱,可以不使用并联的电容或者换用较小的电阻。

2、准确的测量内存时钟需要足够带宽的示波器和探头,无源探头在高频时阻抗太小,不能准确的测量波形,需要使用高带宽的有源探头。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码