解决串行接口中的信号完整性问题

一直以来,信号完整性都是模拟工程师考虑的问题,但是随着串行数据链接的传输速率向GHz级发展,数字硬件设计人员现在也必须关注这个重要的问题。

目前,芯片之间的高速串行链接已经获得了广泛的应用,用于提高较窄的总线带宽的吞吐量。一些最新的DSP和处理器已经开始采用串行RapidIO对于很多硬件设计人员来说,芯片间通讯使用超过300MHz的总线速率是一个新的挑战,而设计出GHz级数据传输速率的高质量数据链接则要求更多的细心和了解,才能确保电路板设计和噪音不会损害到性能。

本文探讨设计人员可能会面临的一些信号完整性(SI) 问题和注意事项,重点介绍他们面临的问题,并提出一些建议。为了举例说明如何应用这些原则,本文介绍了一种16 端口串行RapidIO交换机。

注意事项

信号质量非常重要,在串行RapidIO 中,它是通过接收眼的大小和形状来量化的。接收眼是一种无限延续的轨迹,在接收眼中,波形会随着上一个轨迹不断延续(图1)。如果信号路径中吸收了噪音或其它随机信号,便会引起信号抖动和接收眼收缩,从而导致信号质量下降。

图1 包含一个接收眼图的范围轨迹

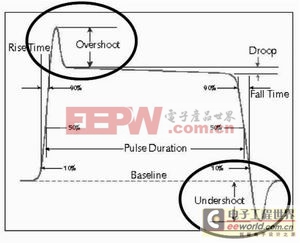

图2 脉冲过冲和下冲的典型特征

在超过300MHz 的频率上,适用于较低频率电路板设计的大部分最佳做法都需要修改。FR4材料或许还能够成功用作基础材料,但是在更高的频率上,则需要在阻抗计算和轨迹建模中重新考虑材料的介电常数和损耗系数。通孔通路的设计也变得十分重要,因为未使用的管状长度会表现出同较厚的电路板和背板不匹配的阻抗。请贴出设计模拟以便对性能进行检验,并注意信号完整性不太理想的路径,同时指出串音区域。

阻抗不匹配造成的反射会导致形成差分对的信号线(图2)出现过冲、下冲和振铃,以及接收眼缩小。

布线层的变更、跳出路径设计不当和连接器选择不当也会造成信号中产生不匹配的人为干扰。串行RapidIO 接口的阻抗要求是100Ω差分。建议的构造方法是采用边缘耦合差分带状线(或称共面带状线),图3 显示的正是这种方法,图中同时提供了单端和差分阻抗的方程式。布线时应当最大限度地减少在不同层之间的转换。除了BGA 衬垫之外,通常每个路径最多允许两个通路。

回流电流路径的定义是电流回到出发点时经过的路径- 通过地层、电源层、其它信号路径以及通过IC。返回路径的完整性可通过绘制一个追踪电流从驱动器经信号导线到达接收器的环路来进行评估- 循环的区域越小,产生的自感应系数也越低。

以下设计规则适用于所有的返回路径。

-不要通过参考层的裂口传送受阻抗约束的信号。

-不要在参考层上传送信号。

-更改信号层不能强迫返回路径对参考层进行更改。如果必须对参考层进行更改,请从一个VSS 参考层更改到另一个VSS 参考层,并在尽可能接近信号通路的地方放置一个连接这两个层的通路。此规则同样也适用于从一个VCC 层到另一个VCC 层进行参考层更改。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码