一种高速EM CCD 图像传感器CCD97时序驱动电路的设计方法

2. 2. 1 I Φ, S Φ, RΦ 驱动设计:

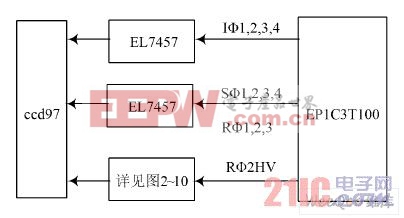

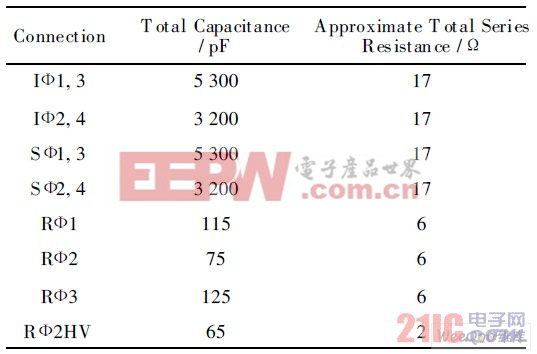

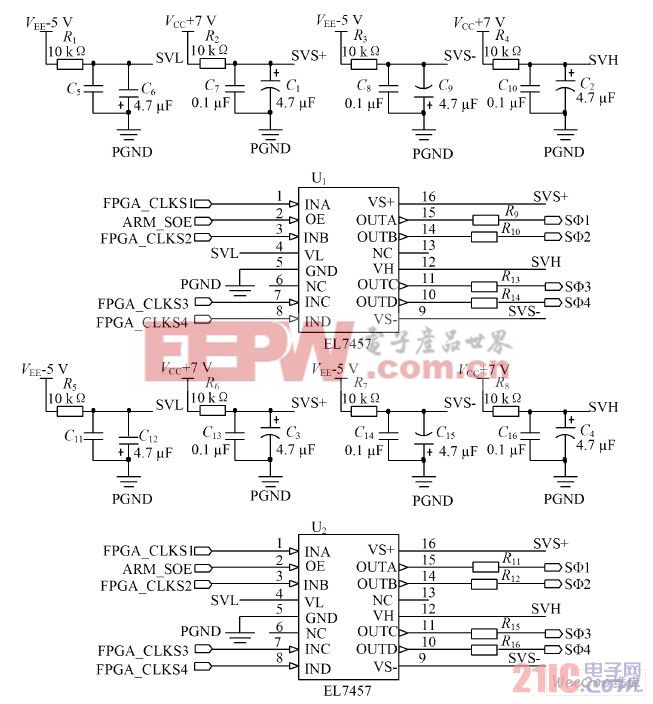

在设计I Φ, SΦ 以及RΦ驱动电路时, 统一采用Elantec 半导体公司的EL7457。它是高速四通道CMOS 驱动器, 能工作在40 MHz, 并提供2 A 的峰值驱动能力, 以及超低的等效阻抗( 3Ω ) , 它具有3 态输出, 并通过OE 控制, 这对于CCD 的驱动来说, 容易实现灵活的电源管理。为了简化设计, 固定RΦ2HV 的电压幅值为典型值。在组成IΦ和S Φ 的驱动电路时必须考虑CCD97 驱动端的等效电容和电阻, 如表2 所示。

图5 CCD97 驱动电路结构原理框图

表2 CCD97 驱动端等效电容及电阻

电路的时间常数:

又因为上升时间与时间常数的关系为:

为了满足最佳上升时间( 200 ns) 的要求, 必须在EL7457 驱动输出端串上一个小电阻, 原理如图6 所示。

图6 中, FPGA _ CLKI1, FPGA _ CLKI2, FPGA _CLKI3, FPGA _ CLKI4 为FPGA 产生的T T L 时序。

ARM_IOE 为ARM 核产生的门控信号, 用来控制驱动脉冲I Φ1, 2, 3, 4 的开关。由于理论与实际计算的误差, 输出串接电阻R9 , R10 , R 13 , R14 将通过硬件调试过程确定, 以产生驱动CC97 工作的最佳波形。同理, FPGA_ CLKS1, FPGA _ CLKS2, FPGA _ CLKS3, FPGA _CLKS4 为FPGA 产生的TT L 时序。A RM _SOE 为ARM 产生的门控信号, 输出串接电阻待定。

图6 IΦ 1, 2, 3, 4; SΦ 1, 2, 3, 4 驱动产生

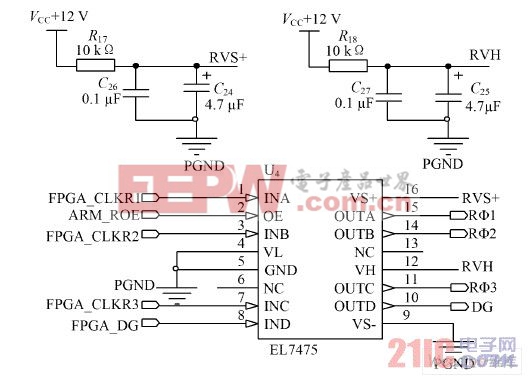

在RΦ1, 2, 3 产生电路中, 因为其电压摆幅要求为0~ 12 V, 故给它加以12 V 的电源( 见图7) 。

图7 RΦ1, 2, 3 驱动产生电路

它的驱动频率为11 MHz, 输出的上升时间不需要串接电阻调节, 可达10 ns。同理, FPGA_CLKR1, FPΦGA_CLKR2, FPGA_CLKR3 为FPGA 产生的10 MHz的驱动时序, ARM _ROE 为ARM 产生的门控信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码