一种高速EM CCD 图像传感器CCD97时序驱动电路的设计方法

EMCCD ( E lectr on Mult iply ing Charg e Co upledDevice) 是新一代高质量微光成像器件。与传统CCD( Charg e Coupled Device) 相比, 它采用了片上电子增益技术, 利用片上增益寄存器使图像信息在电子转移过程中得到放大, 这使得它在很高的读出速率下仍具有相对很低的读出噪声, 能在微光源下高分辨力成像。

EMCCD的这些特性使其在航天微光目标探测、微光生命科学成像、军用高性能夜视探测等领域具有极大的应用潜力。EMCCD 驱动电路是EMCCD 应用的核心技术, 其性能直接影响到成像质量。目前常用的时序产生方法有以下几种:

( 1) 直接数字电路驱动法。这种方法原理简单, 容易实现。但是逻辑设计较复杂, 调试非常困难, 而且在实际电路中因使用芯片较多, 为整个系统带来不可靠性。

( 2) MCU 驱动法。该方法是通过编程MCU 的I/ O端口来获得CCD 驱动脉冲信号的。这种方法的灵活性好, 精度也可以很高, 对不同的CCD 器件只需要修改程序即可。由于CCD 的驱动频率为MHz 级, 使得选用MCU 器件的工作频率必须很高( 提高了硬件成本) , 同时因频繁的中断和任务调度使MCU 效率很低。

( 3) EPROM 驱动法。这种驱动电路一般由晶体震荡器、计数电路和EPROM 存储器构成。这种驱动时序产生方法, 结构简单、明确, 调试容易, 缺点是结构尺寸太大, 对于实现复杂的驱动时序有较大困难。

( 4) 专用IC 驱动方法。这种方法就是利用CCD专用IC 来产生时序, 集成度高, 功能强, 使用方便。对摄像机等视频领域应用的CCD 或三元彩色CCD, 这种驱动方法是首选。一般由相应的CCD 厂家提供。

另一种更有效的方法就是使用CPLD, FPGA 等大规模可编程逻辑器件实现。通过对该逻辑器件的编程,能实现任意复杂的时序逻辑, 且调试方便, 只使用一片集成电路以及少数外围器件, 故可靠性高。本文即采用这种方法, 实现了CCD97 所需的12 路驱动时序。

1 CCD97 简介

CCD97 是E2V 公司的背照式低照度CCD 图像传感器, 有效像素512 × 512, 像素大小16 μm × 16 μm, 它是帧转移型CCD, 芯片采用反向输出模式抑制暗电流,其灵敏度高, 噪声控制方面精益求精, 由于采用新的输出放大电路, 使它能在11 MHz 的像素读出速率下, 以低于1 电子/ 像素的超低噪声工作, 其量子效率高达92. 5%。它获取图像速度快, 具有正常CCD 和EMCCD双读出模式。在微光成像系统中更具有优越性, 能实现真正意义上的24 h 实时监控。

2 驱动电路的设计

2. 1 CCD97 驱动电路的要求

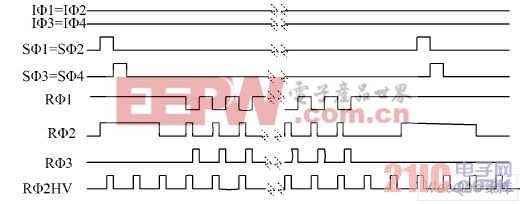

成像区向存储区的转移波形如图1 所示。

图1 成像区向存储区的转移波形

信号电荷在增益寄存器中的转移波形如图2 所示。

图2 为信号电荷在增益寄存器中的转移波形, 转移脉冲RΦ2HV 的高电平必须先于RΦ1 和RΦ2 到达, 同时RΦ1 和RΦ2 需要交替变化。

图2 增益寄存器信号电荷转移时序相位关系

帧转移时序如下:

IΦ 与SΦ 为帧转移脉冲, RΦ1, 2, 3 为行转移脉冲。IΦ 与SΦ 的典型工作频率为1 MHz, R Φ 的工作频率为11 MHz。

在I 1, 2 和I 3, 4 反向时序下, 将成像区图像信号逐行转移至存储区。需要转移的行数为512+ 8+ 8= 528。

行转移时序图:

与帧转移结束, 在转移时序R 1, 2, 3 以及R HV的时序作用下, 存储区的图像以行为单位进行转移, 逐像素通过移位寄存器组, 然后从读出放大器读出( EMCCD读出模式) , 其操作时序如图3 所示。

图3行转移时序图

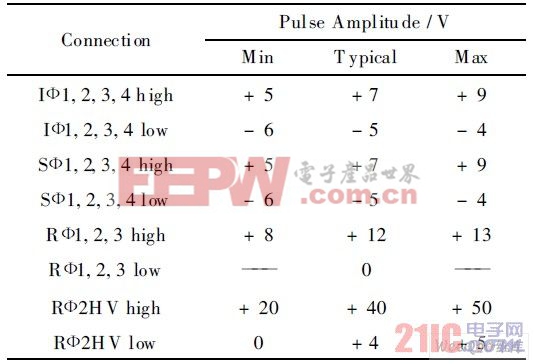

CCD97 所需的电压和波形如表1所示。

表1 CCD97 时序信号的电压需求

由CPLD, FPGA 等可编程器件发生的时序逻辑冒充为TT L 型, 要想它能驱动CCD97 工作, 必须按照表1进行电平转换。

2. 2驱动电路的设计:

该系统选用的FPGA 芯片为Altera 公司Cyclone系列的FPGAEP1C3T 100, 其有100 个管脚封装, I/ O的电源为3. 3 V , 内核电压为1. 5 V, 有1 个锁相环( PLL) , 2 个专用全局时钟输入管脚CLK0、CLK1, 5 个双重用途时钟管脚DPCLK。EP1C3T100 是SRAM 型的可编程逻辑器件, 本身并不能固化程序, 因此需要通过一片FLASH 结构的配置芯片来存储逻辑配置信息。

从Altera 公司提供的数据手册, 可知Cy clo ne 系列的FPGA 仅支持EPCS1, EPCS4 以及EPCS16。而选用的EP1C3T 100 中, 其原始二进制文件大小为627 376 b, 使用EPCS1( 1 048 576 b) 的配置芯片。使用EPCS 配置芯片在主动串行模式( A S) 下( MSEL[ 0. . 1] 置地) , 即可实现上电后, 将存储器件中的数据传送到EP1C3T100 中。系统通过ARM 加载驱动程序实现对FPGA 的配置, 驱动FPGA 产生CCD 的工作时序。本系统选用Atmel 公司的AT 91RM9200 的处理器。它是基于ARM920T 内核, 主频为180 MHz, 运行性能可达200 MIPS, 拥有独立的16 KB 指令和数据Cache, 并配备有16 KB 的SRAM 以及128 KB的ROM。

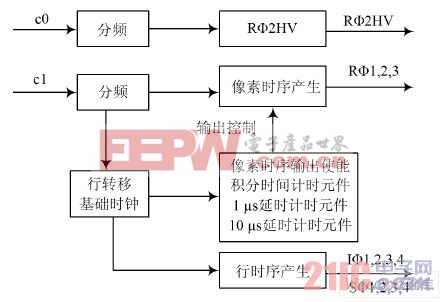

EP1C3T 100 芯片内含1 个PLL, 外接40 MHz 有源晶振为PLL 提供时钟。时钟模块通过Quartus 的megafunct ions 下的altpll 配置生成。采用非补偿模式, 输入/ 输出时钟比为5 :1, 输出的2 路时钟c0, c1 均为200 MHz。其中c0 为clk_gen 模块提供基础时钟。

同时c1 产生相位需要调整的RΦ2HV, 用以满足CCD97 增益寄存器转移过程中的严格时序要求。

在FPGA 时序发生设计中, 依照CCD97 工作的流程, 进行逆序设计。从最高频率的像素移位读出时钟到行转移时钟最后到帧转移这样的流程进行设计。框图如图4 所示。

图4 驱动时序设计框图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码